基于Blackfin的網絡視頻壓縮系統設計

摘要:利用視頻解碼芯片ADV7183A來完成模擬視頻信號的采集量化,進而由ADSP-BF561完成視頻數據的壓縮,再通過PPI傳輸將壓縮過的視頻數據傳送到由ADSP-BF537和LAN8187等芯片組成的網絡傳輸模塊,網絡傳輸模塊再將處理后的視頻數據流通過組播和單播方式發送給指定用戶。能夠滿足觀頻監控系統的實時性和遠程化要求。

關鍵詞:BF561;ADV7183A;視頻壓縮;網絡傳輸

隨著視頻社會的發展和科技的進步,視頻信息業務得到快速增長,視頻信息技術經歷了由模擬到數字的轉變,數字視頻是以數字形式記錄的視頻,數字化對視頻信息的傳輸和存儲創造了有利條件,但末處理的數字視頻流有較高的帶寬,因此在保證視頻圖像清晰度、流暢度、實時性的條件下,進行視頻縮和網絡傳輸成為一項重要的技術。

1 設計方案

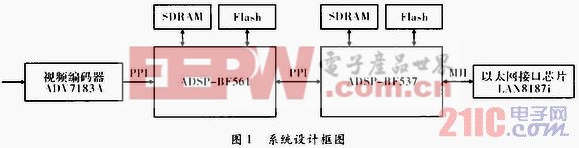

文中網絡視頻壓縮硬件系統結構如圖1所示。在本網絡視頻壓縮系統中,采用Analog Device公司的ADSP-BF561、ADSP-BF537、ADV7183A心片;SMSC公司的LAN8187網絡芯片;系統可分為視頻采集壓縮模塊及網絡控制模塊,其中視頻采集壓縮模塊由ADI高性能雙核處理器DSP BF5 61和視頻解碼芯片ADV7183A構成,并輔以SDRAM和Flash等外圍器件。網絡控制模塊由ADI高性能DSP BF537和以太網接口芯片LAN8187構成,同樣輔以SDRAM和Flash等外圍器件。前端輸入的模擬視頻信號經過視頻解碼芯片ADV7183A采集量化變換為數字視頻信號,通過BF561的并行PPI接口進入BF561的緩沖存儲區,由BF561完成覦頻數據的壓縮處理,壓縮形成的MPEG4視頻流通過并行PPI接口進入BF537,經過封裝處理后通過以太網接口進行分發。

2 硬件電路設計

2.1 視頻采集壓縮模塊設計

視頻采集壓縮模塊由核心壓縮處理器BF561和前端視頻解碼器ADV7183構成,并輔以外圍的SDRAM和Flash。

(1)視頻壓縮處理器BF561。BF561處理器是Blackfin系列中的高性能產品,BF561的核心由兩枚獨立的Blackfin處理器組成。BF561集成了一套通用的數字圖像處理外圍設備,為數字圖像處理和多媒體應用創建了一個完整的系統級片上解決方案。利用BF561雙核結構,將前端視頻解碼器采集的視頻信號分割為上下半幀數據,并將分割的視頻數據分別由其雙核獨立進行壓縮處理,為完整地恢復壓縮前的畫面,在其雙核之間進行了同步處理,使得根據輸出的數據信息解碼后能夠完整流暢的恢復壓縮前的畫面,同時為平衡兩個內核工作量,還將系統的初始化、控制前端視頻解碼器等工作交給主核來處理,給視頻畫面疊加動態輔助信息的工作交給另一個內核進行處理。

(2)視頻解碼器ADV7183A ADV7183A是美國摸擬器件公司(ADI)推出的集成了10位ADC的增強型視頻解M碼器。它內含3個精確模數轉換器(ADCs)和完整的自動增益控制(AGC)電路。其靈活的數字式輸出接口能夠與BF561的PPI接口進行無縫連接,消除了由于數據信息傳輸速度造成整體壓縮處理能力的瓶頸。ADV7183A與DSP之間的配置通信遵循I2C協議,因此ADV7183A提供了標準I2C接口,與BF561的PF接口相連接。

BF561的PF,引腳和ADV7183A的0E引腳相連,控制視頻解碼器的數據輸出,這里輸出的數據可以選擇16/8位輸出,系統選擇8位輸出數據格式;

BF561的PF2引腳和ADV7183A的SDATA引腳相連,ADV7183A的SDATA引腳是I2C總線的串行數據輸入/輸出引腳;

BF561的PF0引腳和ADV7183A的SCLK引腳相連,ADV7183A的SCLK引腳是I2C總線的串行數據輸入/輸出引腳,為視頻解碼器提供串行時鐘輸入;

BF561的PPI2CLK引腳和ADV7183A的LLC1引腳相連,由ADV7183A的LLC1引腳為BF561提供視頻像素輸出同步時鐘;

BF561的PF13引腳和ADV7183A的RESFT引腳相連,為視頻解碼器提供復位信號;

BF561的PPI2D0~7引腳和ADV7183A的,P8-P15引腳相連,作為視頻數據傳輸總線。

同時為ADV7183A提供27 MHz的晶振輸入列XTAL引腳,選擇模擬輸入通道AIN1,在AIN1引腳上輸入模擬信號,對于系統而言,采取默認配置,不再對I2C總線進行配置。完成這些設置后,接上電源,ADV7183A就可以在默認配置下正常工T作了,默認輸入為PAL制的圖像,輸出是P8~P15的8位ITU—BT656的YCrCb型4:2:2視頻數據。

tcp/ip相關文章:tcp/ip是什么

紅外熱像儀相關文章:紅外熱像儀原理

評論