電力電子裝置控制系統的DSP設計方案

在現代高性能電力電子和交流電機控制系統中,DSP已經取代了微控制器成為控制器的核心。其快速強大的運算和處理能力以及并行運行的能力,滿足了電力電子裝置控制系統對實時性和處理算法復雜性的要求,并為不斷發展的新理論和新算法的應用奠定了技術基礎。

C240x系列DSP是面向數字控制系統的新一代數字信號處理器。該控制器集實時處理能力和控制器設計功能于一身,為控制系統應用提供了一個理想的解決方案。其內部的哈佛結構使數據空間和程序空間分離,獨立的數據總線和程序總線允許程序數據同時操作;專用的硬件乘法器極大提高了運算速度;具有獨特的逆尋址方式,能高效地進行快速傅里葉變換運算;指令系統采用流水線操作,減小了指令周期;采用內存映射方式管理I/0,能靈活方便地擴充外圍電路。

1 主電路硬件設計

1.1 系統總體設計

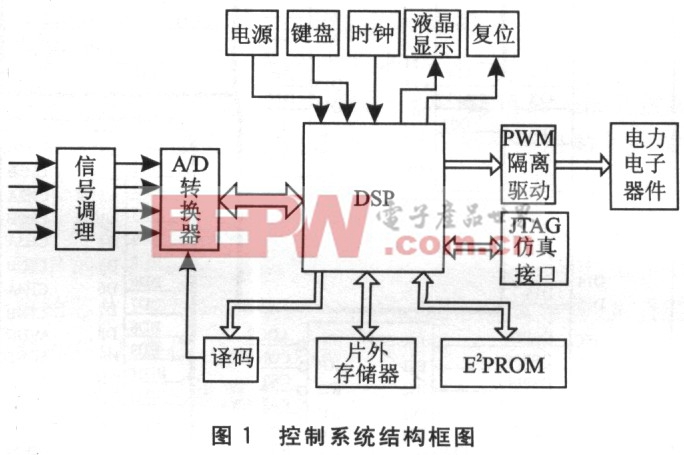

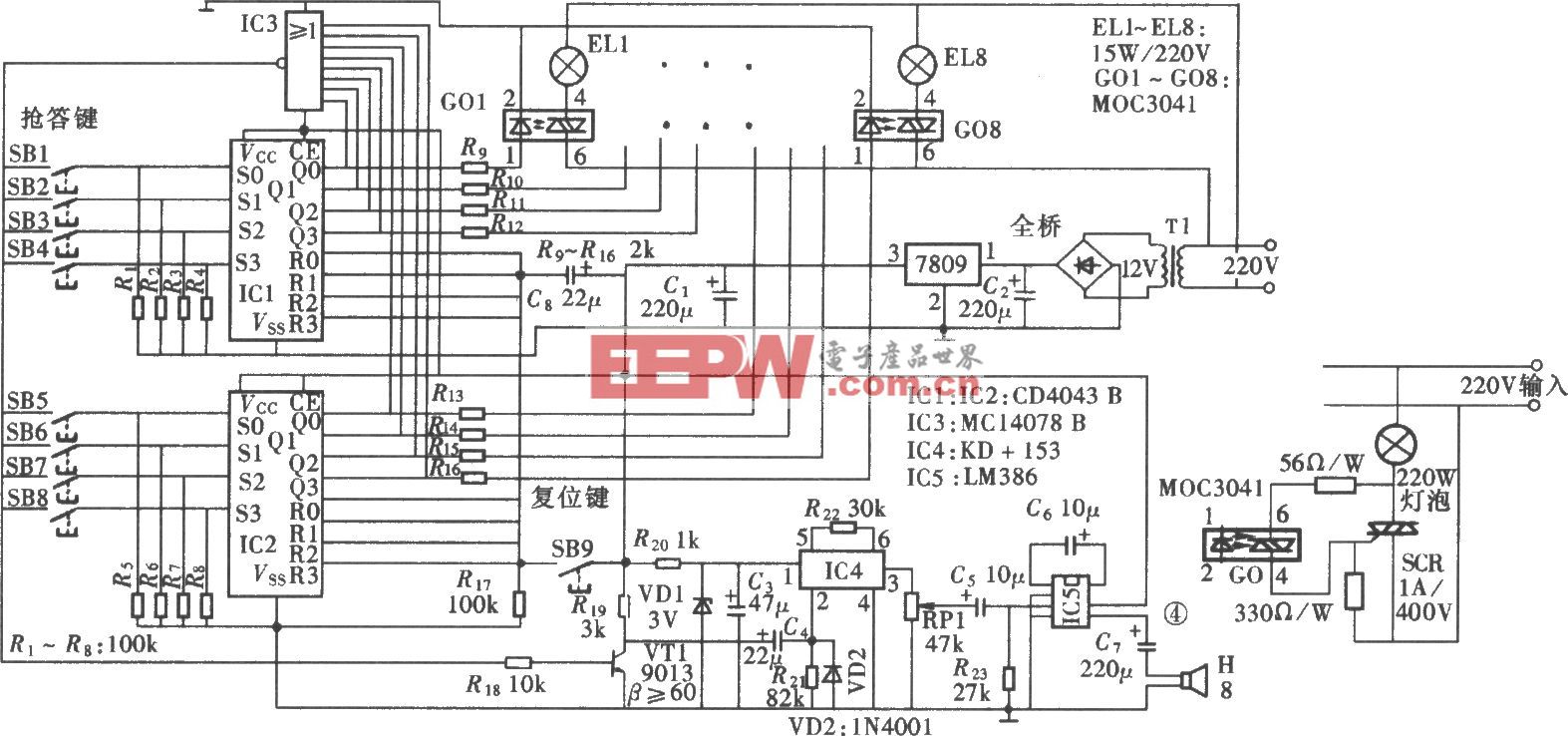

一般電力電子裝置控制系統的總體結構如圖1所示。詳細介紹各單元的功能與硬件電路。

1.2電平轉換

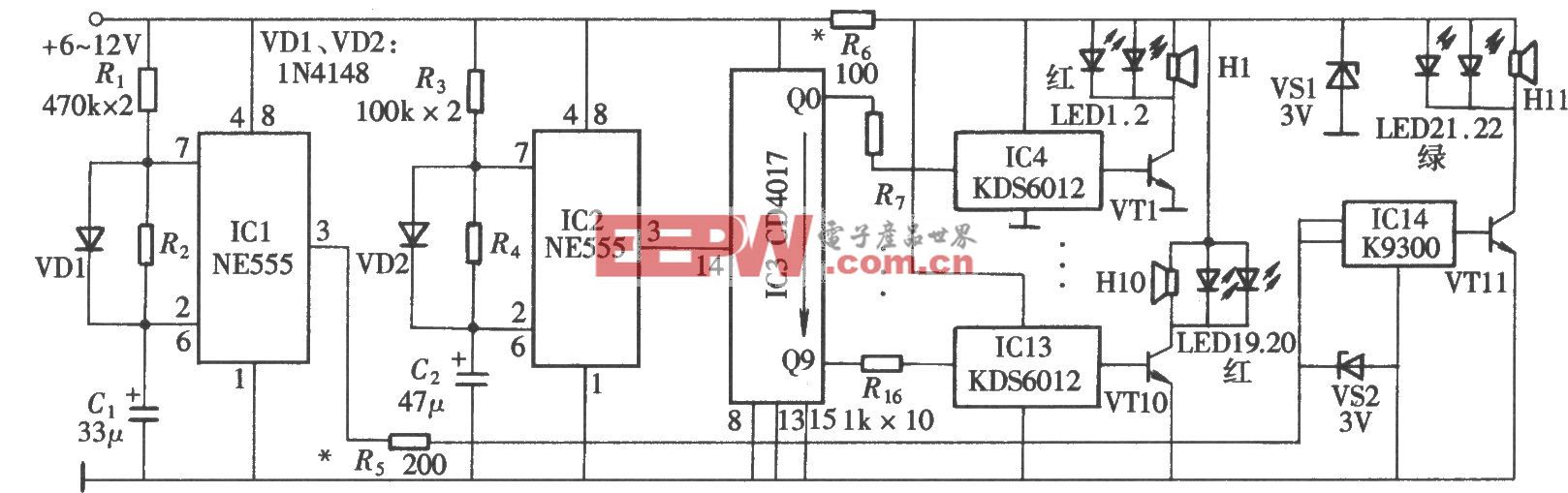

TMS320LF2407a(以下簡稱2407a)采用3.3V電,減小了芯片功耗;但常用直流電源為5V,因此必須考慮電平轉換問題。一種方法是直接采用可調直流電源獲得3.3V電壓,但這樣很難保證電源電壓的穩定性,影響DSP的正常運行。另一種方法是采用專門的電源芯片,將5 V電壓降為3.3 v。TPS76833、TPS76HD318、MAX604為常用的電平轉換芯片。圖2為采用MAX604實現電子轉換的電路。并聯于電源與地之間的電容起穩壓作用。

1.3 時 鐘

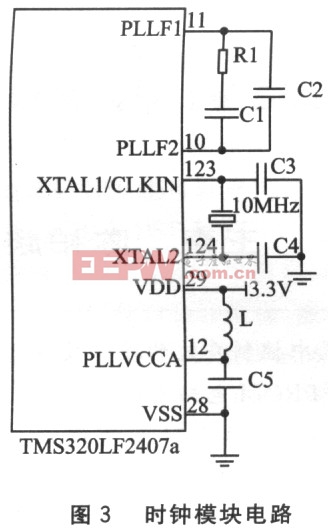

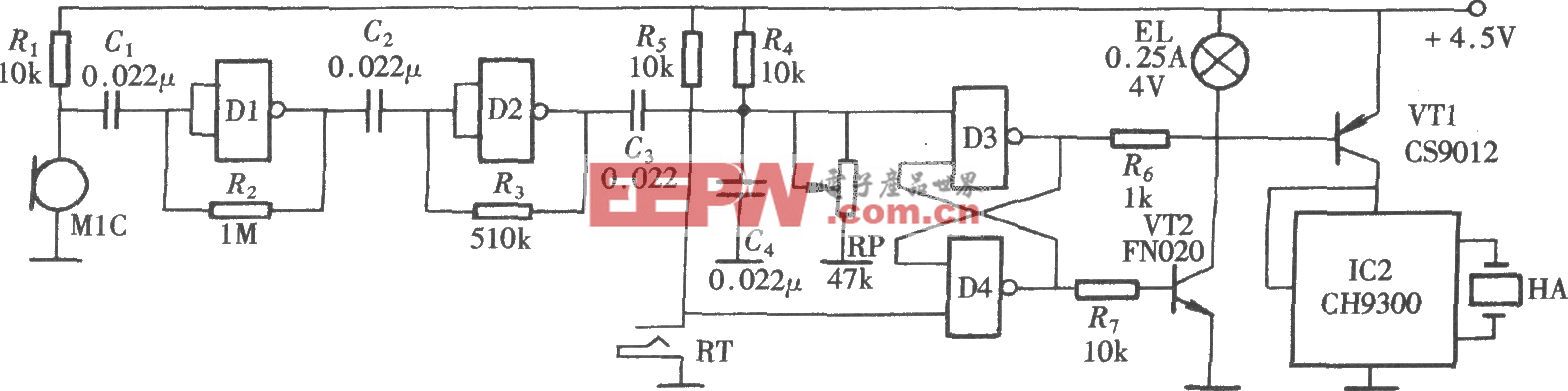

與一般微處理器不同,C240x系列DSP利用掛接在片內外設總線上的鎖相環時鐘模塊(PLL)合成系統需要的各種時鐘信號(CPU時鐘、系統時鐘、模擬時鐘和看門狗時鐘)。外部時鐘信號經PLL倍頻后合成系統時鐘頻率。如圖3所示,外部時鐘信號由lO MHz晶振提供,通過系統控制和狀態寄存器(SCSR1)設置4倍頻因子后,2407a DSP以最大時鐘頻率(40MHz)工作。通過檢查DSP時鐘輸出引腳(CLK0UT)的頻率,可以判斷DSP芯片是否已開始正常工作。PLL模塊使用外部濾波器回路來抑制信號抖動和電磁干擾。濾波器回路由PLL接在濾波器輸入引腳PLLF和PLLF2之間的電阻Rl和電容Cl、C2組成。電容Cl、C2必須為無極性電容。在不同的振蕩器頻率下,R1、Cl、C2的取值不同,常用的參數組合如表l所列。PLL模塊的電源引腳PLLVCCA分別通過磁珠和0.1μF的電容與數字電源引腳VDD和數字地引腳VSS連接,構成低通濾波電路,保證時鐘模塊的可靠供電。

1.4 片外存儲器

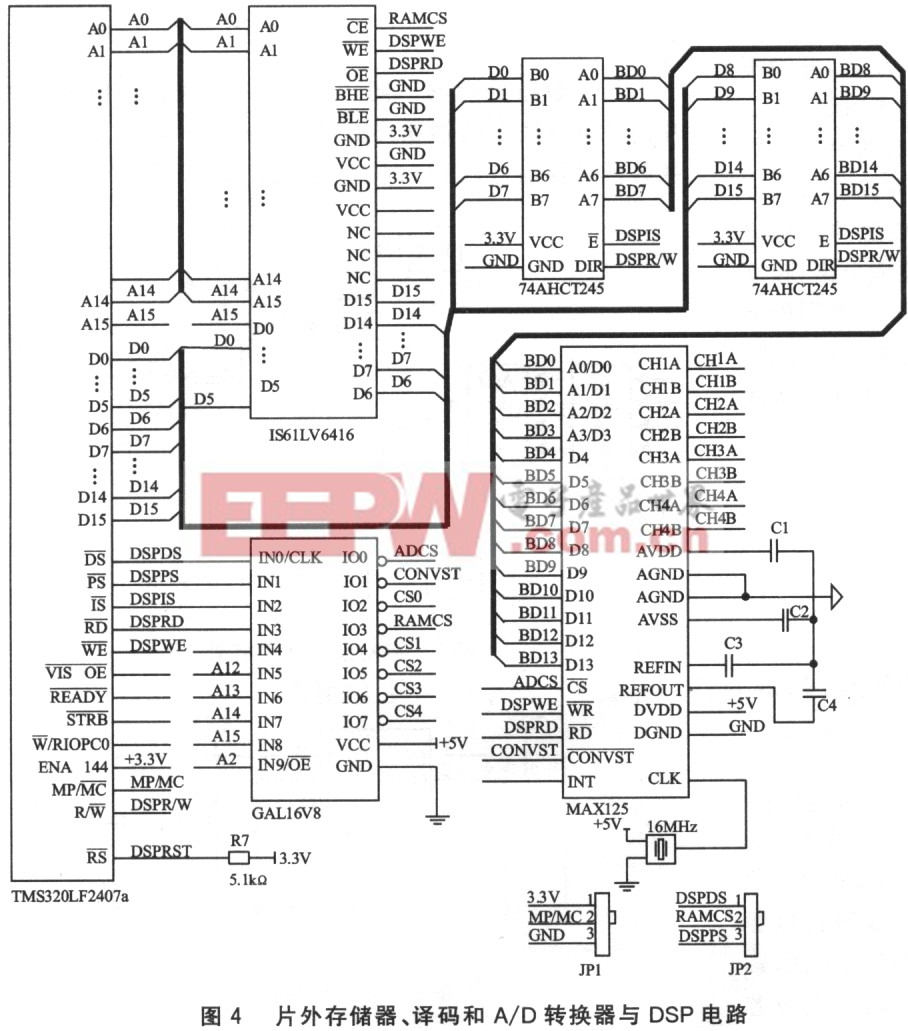

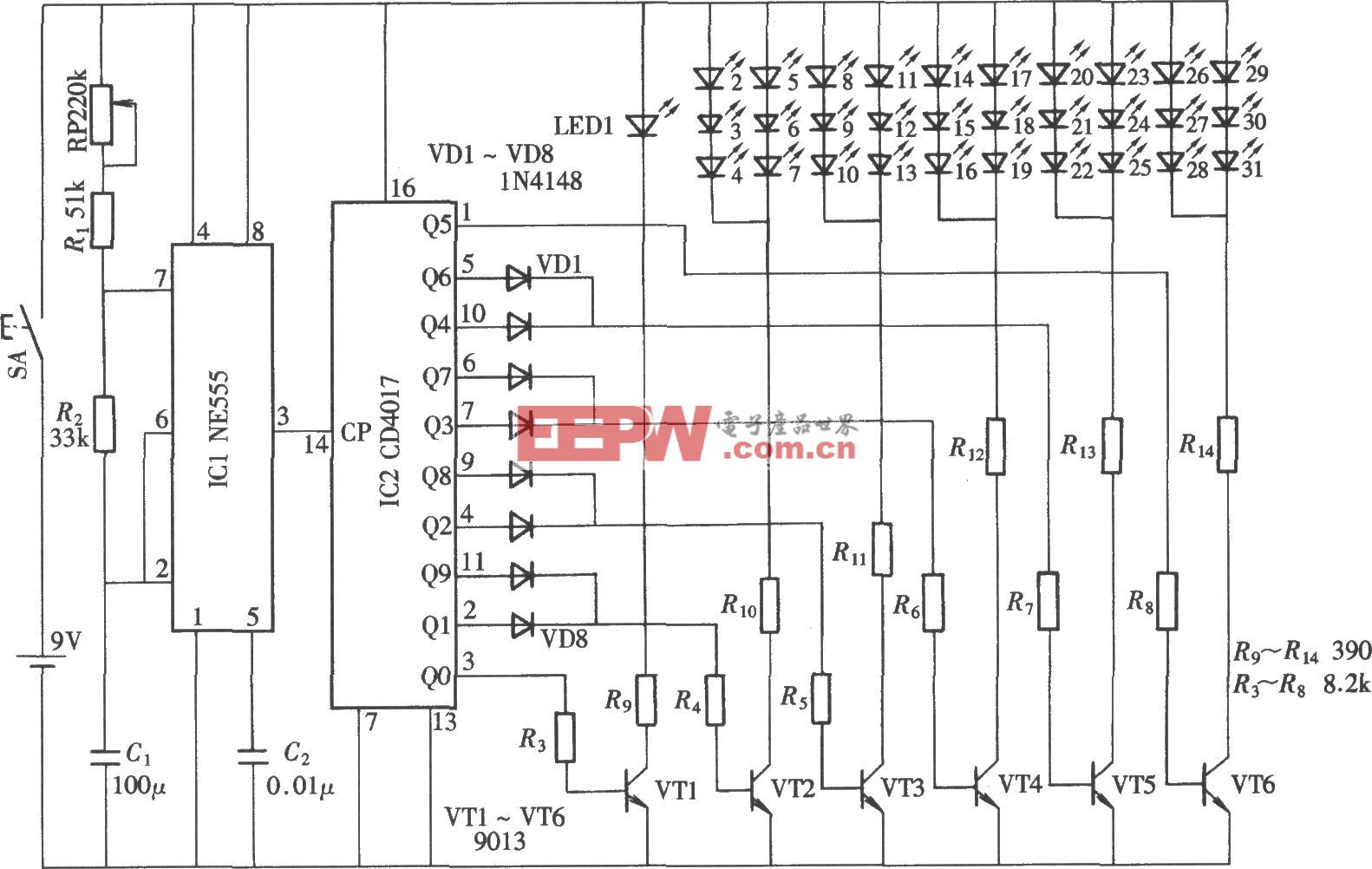

2407aDSP可以訪問的程序存儲空間為64K字,根據MP/MC引腳的電子決定其配置方式。當MP/MC為低電平時,片內Flash存儲空間使能,地址范圍是0000h~7FFFFh,8000h~FFFFh的地址留給外部程序存儲器。當MP/MC為高電平時,片內Flash被禁止,64 K字存儲空間全部位于外部程序存儲器中,即只能從片外存儲器中讀取數據,使得仿真調試時通過仿真器對程序修改比較容易。2407a DSP有64K的16位數據存儲器空間,32 K字的內部存儲器地址范圍是0000h~7FFFh,包括存儲器映射寄存器、DARAM和外設映射寄存器。另外,地址范圍是8000h~FFFPh的32 K字留給外部數據存儲器空間。片外存儲器的選擇主要考慮電壓、容量、速度等指標。本文采用工作電壓3.3 V,容量64K×16位,訪問時間15 ns的高速靜態RAM,IS6lLV6416-15T作為片外存儲器。如圖4所示,片外存儲器的數據、地址線分別與DSP對應相連;輸出使能引腳OE和輸入使能引腳WE分別與DSP的讀選通DSPRD相連。仿真調試時,用跳線把片選引腳DSPWE與DSP的程序空間選通引腳CE相連,當外部程序存儲器用。程序燒寫到片內Flash后,把片選引腳CE與DSP的數據空間選通引腳DSPDS相連,當外部數據存儲器用。

評論