數字合成掃頻儀USB2.0接口設計

摘要 在對數字合成掃頻儀的硬件設計進行概述的基礎上,描述了一種基于ISP1362的USB2.0接口設計方案,包括USB接口的硬件結構設計,USB固件程序、驅動程序以及應用程序的設計方法?實驗表明,整個設計滿足設計要求,傳輸速率可達33 Mbit·s-1。

關鍵詞 掃頻儀;USB2.0;ISP1362

數字合成掃頻儀的USB接口設計,分為硬件和軟件兩部分,硬件包括掃頻儀主體和USB接口兩部分,設計選用Philips公司的ISP1362作為USB接口芯片,該芯片支持USB2.0全速模式,支持OTC模式,芯片由外設控制器、OTG控制器、主機控制器、USB收發器、OTG收發器和緩存器組成,通過內部集成的總線接口可與CPU相連。軟件部分包括接口的底層固件程序、USB設備驅動程序和用戶應用程序。

1 硬件設計

1.1 數字合成掃頻儀電路設計

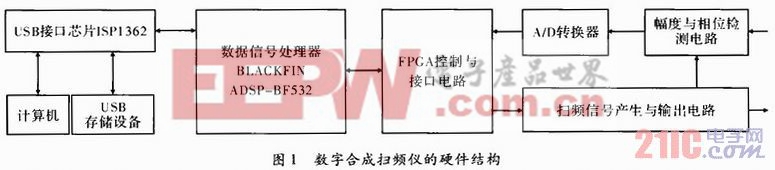

數字合成掃頻儀主要由數據處理、控制接口電路邏輯、掃頻信號產生與輸出、幅度與相位檢測、數據采集、USB接口等部分構成。數據處理部分采用ADI公司的ADSP-BF532處理器,加電后BF532實現對系統各部分的初始化,并對采集到的數據進行處理,得到幅度與相位數據并實現曲線描繪、數據存儲和USB通信;控制接口電路邏輯部分采用Altera的EP1C6T144實現,設計中采用FPGA實現了DDS信號發生控制、數據采集控制、鍵盤掃描、增益控制以及顯示控制;掃頻信號產生與輸出部分包括信號產生部分和輸出增益控制部分,信號產生部分產生兩路I、Q信號,其中I路信號用來實現相位測量,Q路經增益調節后得到所需測量輸出信號;幅度與相位檢測部分將信號的幅度與相位信息轉換為對應的電壓信號;數據采集部分通過采集信號幅度和相位對應的電壓值將幅度與相位信息轉換為數字信息,FPGA將采集到的數據通過SPI口送入DSP處理后得到幅度與相位曲線。

1.2 USB接口電路設計

Philips生產的ISP1362提供兩個USB端口,端口1通過軟件配置可用作上行、下行或OTG端口,若以OTG模式進行配置,ISP1362既可做主機又可做外設,并支持主機與外設之間角色轉換的主機通信協議HNP(Host Negotiation Protocol)和對話請求協議SRP(Session Request Protocol)。ISP作為主機使用時,能夠關閉VBUS以響應SRP,而作為外設使用時,能夠啟動SRP以喚醒主機。設計中BF532通過EBIU接口與ISP1362連接,引出Host和OTG接口,OTG接口又分成一個Host接口和一個Device接口,供接USB外設使用。如圖2所示,其中CPLD為該模塊提供基地址。DSP通過向CPLD寄存器讀入狀態字或寫入控制字將寄存器的地址映射在DSP的I/O空間,通過訪問CPLD中相應的寄存器,可實現對ISP1362狀態查詢和控制。

評論