Cortex-M4內核微處理器DMA方式的高速A/D采樣

1 MK60N512VMD100微處理器簡介

MK60N512VMD100芯片是基于Cortex-M4內核的典型芯片,是飛思卡爾Kinetis系列中集成度最高的芯片。Cortex-M4內核是在Cortex-M3內核的基礎上發展起來的,其性能比Cortex-M3提高了20%。Cortex-M4在Cortex-M3的基礎上強化了運算能力,增加了浮點運算控制器、DSP和并行計算等。MK60N512VMD100具有豐富的通信接口,主頻高達100MHz,32路DMA供外設和存儲器使用,大大提高了CPU利用率,具有33路單路和4路差分的16位A/D轉換器、2路12位D/A轉換器等外設。

2 MK60N512VMD100芯片DMA和ADC介紹

Kinetis系列微處理器都含有DMA,在最小的CPU干預下最高可提供32路DMA供外設和存儲器使用,大大提高了CPU的利用率。DMA通道復用器(類似多路選擇開關)可以把最多63個DMA請求源和16個DMA通道中的任意一個映射到一起。16路獨立可選的DMA通道中,前4路還具有自觸發功能。DMA復用器有3種工作模式:禁用模式、普通模式和周期觸發模式。本文就介紹用周期觸發模式實現高速A/D采樣功能。

DMA通道復用器除了提供正常的映射功能外,前4個通道還提供了周期觸發功能,由周期性中斷定時器(PIT)觸發,這種機制能夠實現在沒有CPU的干預下傳輸字節、幀或數據包。這種觸發功能可用于任何支持DMA傳輸的外設,最常用的應用包括以下兩種情況:

①定期輪詢一個特定的總線上的外部設備。例如:一個SPI總線作為源被映射到DMA通道0,一旦設置成功,只要SPI的發送緩沖區是空的就會請求DMA傳輸,從內存中復制數據到緩存。SPI傳輸通過此通道上的一個觸發器每3μs(舉例)自動執行一次。在SPI接收端,SPI和DMA可配置成把接收到的數據傳到內存,在無需處理器干預的情況下有效地定期從外部沒備讀取數據送到內存中。

②利用GPIO端口產生或者采樣波形。通過配置DMA將數據傳送到一個或多個GPIO端口,可以使用存儲在存儲器中的表格數據產生復雜的波形。相反,使用DMA從一個或多個GPIO端口讀取數據,是可以采樣到復雜波形的,并把數據存儲到內存中。

MK60N512VMD100芯片的ADC模塊具有線性逐次逼近算法與高達16位的分辨率,4路差分1 6位A/D轉換和24路單端外部模擬輸入。輸出模式有差分16位、13位、11位和9位幾種模式,單路支持16位、12位、10位和8位模式,并且輸出無符號數右對齊格式。

當應用程序需要連續采樣時(每秒6 000個采樣點),CPU可能會有相當大的負擔。雖然使用可編程延遲模塊(PDB)可能會減少一些CPU的負載,但是ADC支持DMA請求功能在高速采樣時能獲得更高的性能,ADC在轉換完成后通過DMA中斷請求觸發DMA。本文就介紹此種方法。

3 軟件設計

3.1 DMA周期觸發方式相關寄存器的設置

(1)DMA通道配置寄存器(DMAMUX_CHCFGn)

DMA通道配置寄存器(DMAMUX_CHCFGn)數據格式如圖1所示。

bit7(ENBL):DMA通道使能,設置為0則通道禁用,為1則通道使能。

bit6(TRIG):DMA通道觸發使能,設置為0則觸發禁用,為1則觸發使能。

bit(5:0)(SOURCE):DMA通道源。

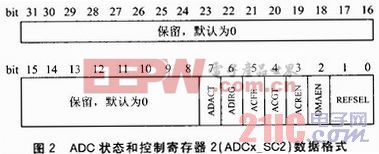

(2)ADC狀態和控制寄存器2(ADCx_SC2)

ADC狀態和控制寄存器2(ADCx_SC2)數據格式如圖2所示。

bit7(ADACT):轉換狀態位,當一個A/D轉換開始時ADACT被置位,當一個轉換完成或中止時ADACT被清零。

bit2(DMAEN):設置為0則DMA功能禁用,為1時DMA使能。當一個ADC完成時發出 ADCDMA請求。

評論