位填充導致USB數據傳輸紊亂的一種解決方案

摘要:通用串行總線(USB)數據傳輸中要對數據進行非歸零翻轉(NRZI)編解碼、添加/去除位填充和串并/并串轉換。添加/去除位填充使每字節數據傳輸所需的時間發生變化,再加上收發器與協議層的時鐘頻率不同,從而可能導致數據紊亂。以USB 2.0設備控制器中的收發器為例,在收發器與協議層間添加異步先入先出存儲器(FIFO)作為緩存區可以解決這一問題。EDA軟件仿真驗證了該方法的可行性。

關鍵詞:通用串行總線;數據傳輸;位填充;異步先入先出存儲器;數據紊亂

在USB數據傳輸中,為了保證數據的可靠性,需要對所傳輸的數據進行NRZI編解碼、添加/去除位填充和串并/并串轉換。NRZI編碼可以保證有足夠的跳變沿在接收端進行時鐘恢復;位填充是為了保證信號具有足夠的變化量;串并轉換可以降低后端數據處理模塊的工作頻率。

以USB 2.0設備控制器為例。在向主機發送數據時,其收發器模塊先要將協議層傳來的8位(或16位)并行數據轉換成串行數據,然后添加位填充(每6個連續的1后要加入一個0),最后進行NRZI編碼。反之,在接收主機發來的數據時,收發器模塊要先對數據進行NRZI解碼,再去除位填充,最后轉換成8位(或16位)并行數據傳給協議層。

USB 2.0設備控制器的收發器和后端協議層的工作時鐘頻率不同。對于具有高速(480 Mb/s)和全速(12 Mb/s)兩種傳輸速度的USB 2.0設備控制器來說,收發器在高速、全速模式下的工作時鐘頻率分別為480 MHz和12 MHz;而協議層在高速、全速模式下的工作時鐘頻率統一為60 MHz(8位并行數據時,對于16位并行數據為30 MHz)。

由于添加/去除位填充導致了每字節數據傳輸所需的時間的增加或減少,再加上收發器和協議層工作時鐘頻率的差別,可能會導致數據的紊亂。

1 數據紊亂的原因分析

假設USB 2.0設備控制器的收發器工作時鐘為clk,協議層使用8位并行數據,工作時鐘為60 MHz的phy_clk,分析數據紊亂產生的原因。

1.1 高速接收模式

USB2.0協議中定義了信號RxValid表示接收數據有效,在phy_clk上升沿,若RxValid=1,協議層可以從收發器提取8位并行數據使用。Rx Valid信號變化后至少需要保持1個phy_clk周期,才能保證其被協議層的phy_clk時鐘采樣。

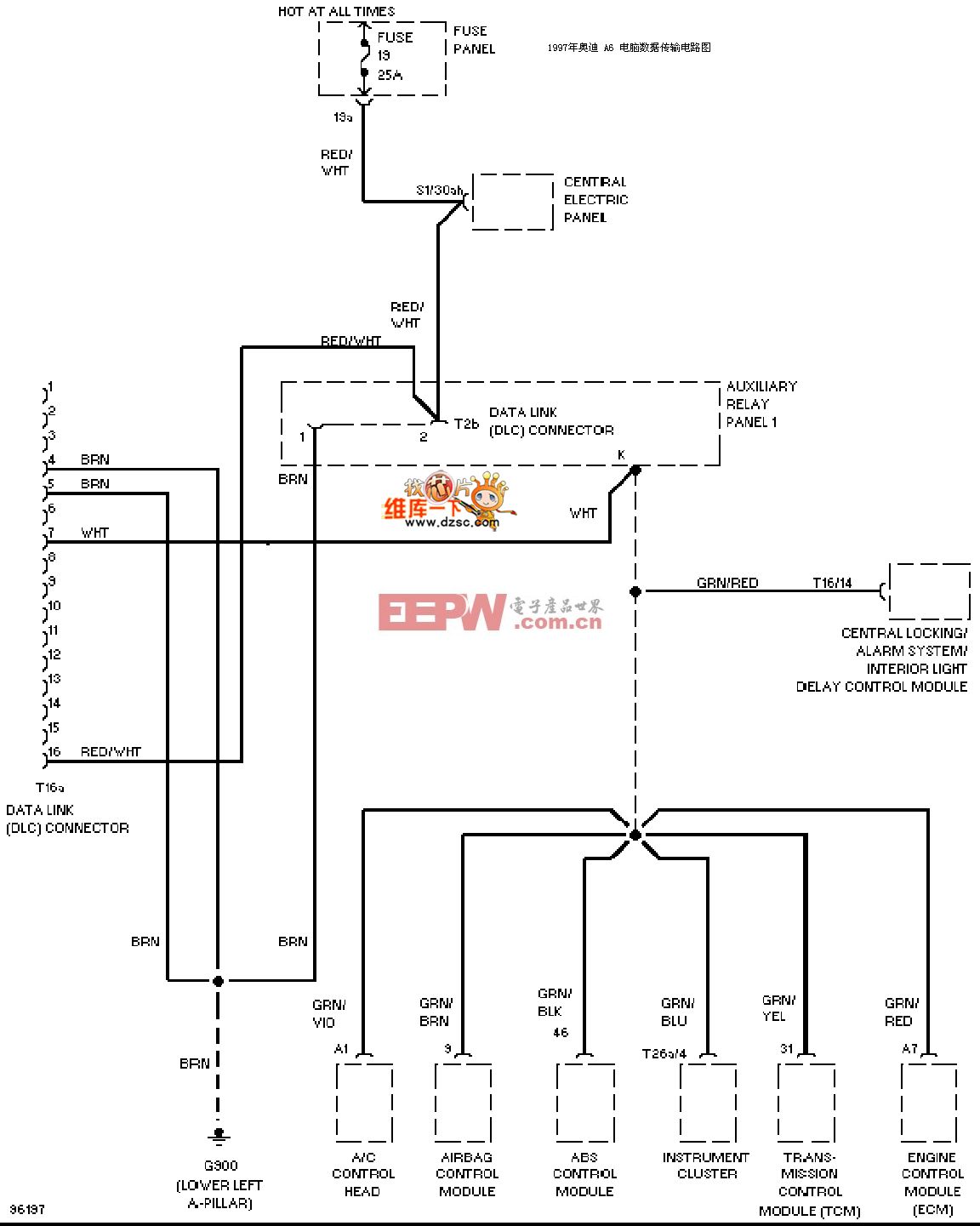

圖1中Data_nrzi為已經過NRZI解碼的串行輸入數據;drop_bit為去位填充提示,當drop_bit=1時說明出現了連續6個數據1,其后的數據0為位填充位應該除去,不放入hold_reg中;Data_nrzi經過去位填充后放入hold_reg中,hold_reg收集了8個Data_nrzi數據后,將這8個數據以并行數據DataIn的形式傳給協議層。

從圖1中可以看出,在處理第二組8位數據時,由于其中有一個位填充需要去除,故處理這組數據用了9個clk周期,導致第一組8位并行數據在DataIn中的持續時間為9個clk周期,比正常多了1個clk周期。這樣有兩個缺點:

1)1個phy_clk周期為8個cIk周期,第1組8位數據持續9個clk周期有可能會被協議層采樣兩次。如圖1中所示,第1組數跨越了兩個phy_clk的上升沿,被采樣兩次。雖然出現這種情況的概率較小,但并不是不存在,且隨著位填充數最的增多,這種多次采樣的可能性會增大。

2)每當位填充的個數達到8個,輸出的DataIn被協議層采樣到的并行數據總量會比正確的情況多1個,從而導致數據接收錯誤。

為了避免上述錯誤,通常的做法是每當去除了8個位填充數據時,就令RxValid=0并持續1個phy_clk周期,使協議層暫停采樣一次,從而避免第2)類錯誤的發生。但這種做法不能完全避免第1)類錯誤的發生。

1.2 高速發送模式

USB 2.0協議中同樣定義了信號TxReady表示收發器準備好發送數據,在phy_clk上升沿,若TxReady=1,協議層便傳輸過來1個8位并行數據讓收發器發送出去。同理TxReady信號變化后也至少要保持1個phy_clk周期。

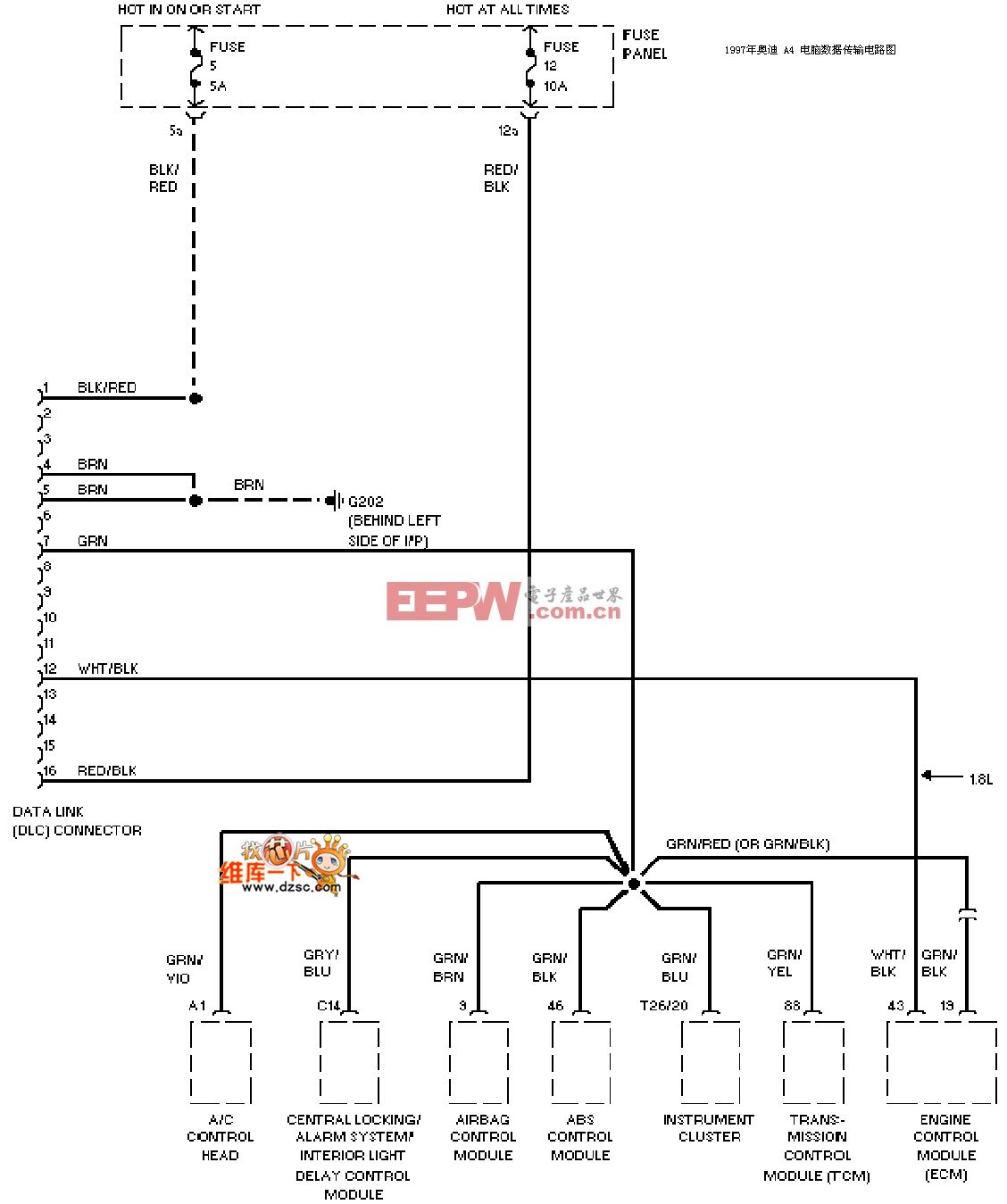

圖2中,TxReady由0變為1代表收發器已將包的同步域發送完畢,開始發送早已從協議層傳來的第1組8位并行數據:DataOut為協議層傳來的8位并行數據;在clk上升沿,將DataOut數據讀取到暫存器hold_reg中;sd_raw為并串轉換后的串行數據;stuff為添加位填充信號,當連續出現6個1時,stuff=1在串行數據中添加1位位填充數據0;sd_bs為添加位填充后的數據,對sd_bs進行NRZI編碼后即可發送給主機。

從圖2中可以看出,高速發送模式出現了兩類錯誤:

1)TxReady由0變為1后開始發送第1組8位并行數據,而當phy_clk上升沿來臨后DataOut和hold_reg先后變為了第2組8位并行數據,此時第1組數據并不一定恰好剛剛發完,于是會造成數據缺失或重復發送,同時使后面的數據發送混亂。圖2中Txready變為1后sd_raw發送的第1個數據1為同步域的最后一位,接著發送的數據00為第1組數據中的2位,其余6位還未發送hold_reg中的數據已變成了第2組并行數據。

評論