基于DVI接口的圖像總線控制系統

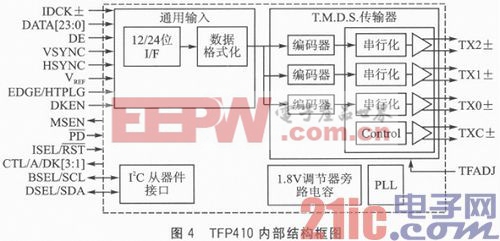

系統采用TI公司的視頻編碼芯片TFP410,編碼后的TMDS信號通過DVI電纜傳送至DVI顯示器。與TFP401對應,TFP410支持從VGA到UXGA(25~1 65MHz)格式的像素速率,具有12位雙邊和24位單邊兩種輸入模式,可以通過I2C總線進行芯片工作模式配置。TFP410主要通過DE引腳的高低電平來決定發送信號類型:當DE為高電平時,發送像素編碼數據;當DE為低電平時,發送同步信號以及控制信號。ISEL引腳的高低決定是否采用I2C總線,ISEL信號為低電平時,需要根據外部引腳對芯片進行配置;當ISEL信號為高電平時,可以通過I2C總線來配置,此時外部引腳配置不起作用。TFP410內部結構框圖如圖4所示。本文引用地址:http://www.j9360.com/article/159314.htm

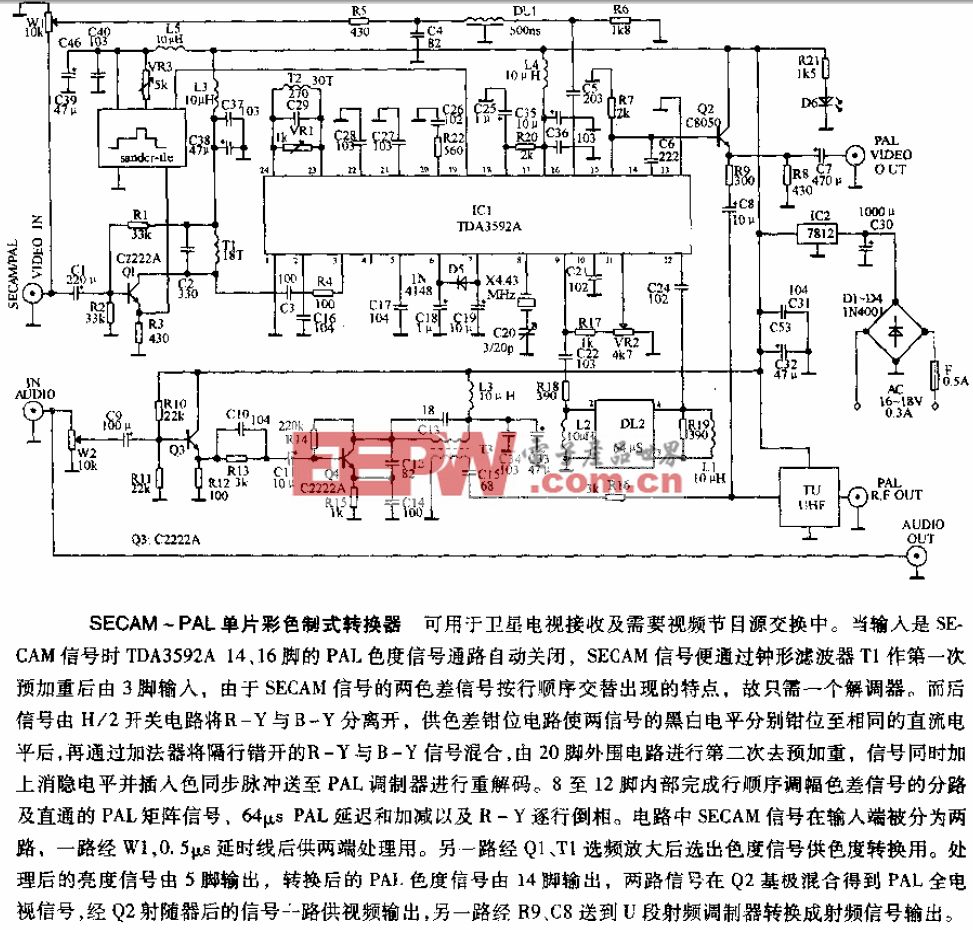

4 CAN總線通信模塊

系統需要和上位機進行通信,采用CAN總線進行數據交互。CAN總線具有通信速率高、開放性好、報文短、糾錯能力和擴展能力強的特點,通信速率可高達1 Mbps,特別適用于實時性要求很高的網絡。

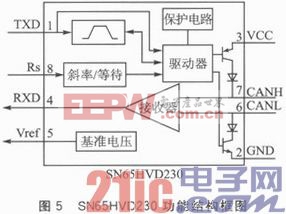

系統采用了集成CAN總線控制器的C8051F系列單片機。通信軟件設計通過KeilC51實現,程序分別實現單片機交叉開關配置與端口初始化、外部振蕩器初始化、CAN總線定時寄存器初始化、消息對象初始化、CAN總線數據發送和接收、消息響應、錯誤處理、系統廣播等功能。SN65HvD230功能結構框圖如圖5所示。

采用TI公司生產的3.3 V芯片SN65HVD230作為總線收發器。該收發器與PCA82C250引腳兼容,具有差分收發能力、高速率傳輸(1 Mbps)、高抗電磁干擾、超小封裝、低功耗等性能;并有3種不同工作模式可供選用,與集成了CAN總線控制器的C8051F系列單片機配合使用,可使外圍電路更加簡潔。

SN65HVD230的CANH和CANL輸出引腳需并聯一個電阻,作為CAN總線的終接電阻,終接電阻需滿足傳輸電纜的特性阻抗,一般取值120 Ω。

SN65HVD230的Rs引腳為斜率電阻輸入引腳,通過改變加在該引腳上的電壓,可以改變收發器的工作方式。

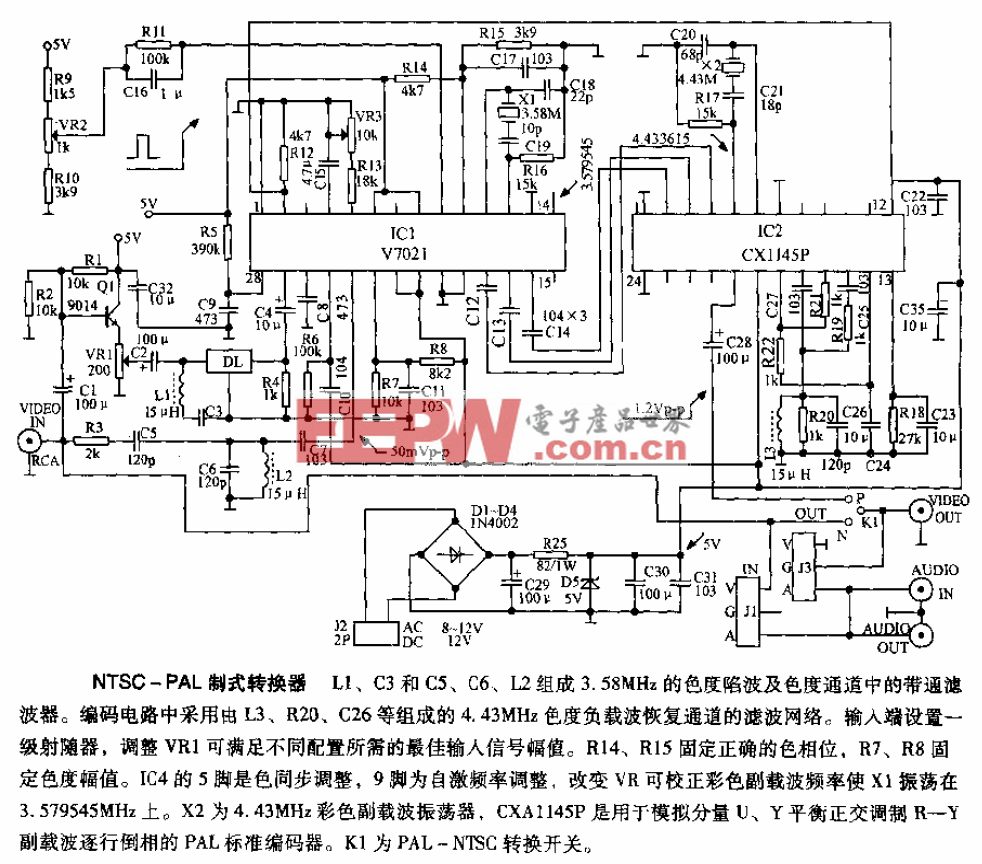

5 PAL模塊

系統提供一路PAL制式模擬信號輸出給TV監視器。由于PAL制式場頻為50Hz,幀頻為25 Hz,所以前端高分辨率高幀頻的數字圖像必須降頻輸出,且分辨率也要降低。PAL編碼芯片選用Philips公司生產的SAA7128,支持PAL/NTSC/SECAM制式的編碼。它可以接受ITU-R BT.656格式4:2:2數據流信號,輸出標準CVBS復合視頻信號。

SAA7128將FPGA送出來的ITU-R BT.656格式4:2:2數據流進行數模轉換,經過視頻矩陣編碼轉換成模擬的視頻信號。該芯片工作在SLAVE模式下,即27MHz數據時鐘由外部振蕩器供給。SAA7128利用此時鐘對數字信號進行鎖存。

系統選用的C8051F系列單片機具有I2C總線功能。可通過I2C總線對SAA7128上電后進行初始化控制。PAL信號的HS行同步,VS場同步信號均由SAA7128自動生成。

FPGA首先在內部建立一個RGB信號到YCbCr信號的轉換表。可在FPGA內部開辟兩片RAM進行乒乓操作,FPGA利用HS行同步、VS場同步來組成ITU-RBT.656格式4:2:2的數字視頻流。PAL一幀傳遞結束時,置一個標志位,SAA7128開始讀其中一片RAM的數據,同時對另一片RAM進行寫操作,寫入一幀新的數據,如此往復。并使TV監視器能夠看到完整的CVBS信號圖像。在FPGA設計時,必須注意PAL信號分奇偶場,采集的信號需要隔行采集,兩場結束才為完整的一幀圖像。

結語

本文從工程應用的角度出發,詳細介紹了基于DVI接口的圖像總線控制系統,該系統能夠采集基于Camlink接口的高速CCD傳送的數字視頻信號,并能通過DVI接口實現1080 P的高清顯示。實踐證明,該系統采集數據穩定、圖像清晰,具有較高應用價值,可廣泛應用于圖像處

理領域。

評論