DS/FH混合擴頻接收機解擴及同步技術的FPGA實現

1 混合擴頻接收機解擴模塊的FPAG設計

本文引用地址:http://www.j9360.com/article/157799.htm解擴模塊是混合擴頻接收機的核心。該模塊實現對接收信號的解擴處理,主要包括數字下變頻器、數控振蕩器(NCO)、碼發生器、相關累加器和偽碼移相電路等,通常各模塊采用專用芯片。利用FPGA將這些功能集成在一塊芯片中,大大縮小了接收機的體積,便于實現系統的小型化和集成化。下面分別介紹該模塊各部分的FPGA實現結構。

1.1 數控振蕩器(NCO)

數控振蕩器是解擴模塊中的重要組成部分,主要用于為碼發生器提供精確的時鐘信號,從而實現對接收信號的捕獲和跟蹤。碼發生器由相位累加器和查找表構成。若使用字長為40位寬的累加器,對于某一頻率控制字A,輸出頻率fout與輸入頻率控制字A的關系為:

其中,fclk為系統時鐘。只要改變控制字A的大小,就可以控制輸出頻率fout。fout變化的最小步長Δf由累加器的數據寬度決定。若數據寬度取40位,則:

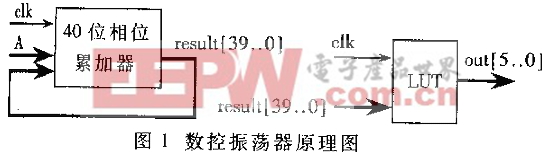

利用上述原理,可以通過精確分頻得到所需頻率。原理圖如圖1所示。

圖1中頻率控制字A由DSP寫入。考慮到FPGA內部存儲資源限制,取40位相位累加值result[39..0]的高八位作為查找表LUT(look-up table)的輸入,查找表由ROM構成,存儲各相位所對應采樣值。當查找表輸入端為某一相位phase時,則輸出對應采樣值。若輸出數據寬度為6位,輸出信號格式為余弦信號,則LUT輸出為[6]:

若取ROM的并行6位out[5..0]作為輸出,則輸出信號為每周期采樣256點的數字化余弦信號;如果取最高位out[5]作為輸出,則輸出為系統時鐘的分頻信號。

1.2 數字下變頻器

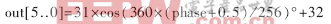

數字下變頻器將A/D采樣得到的中頻信號進行下變頻處理,去除中頻,得到基帶信號。利用本地NCO產生與輸入中頻信號頻率相同的正弦和余弦信號,并與輸入信號進行復乘法運算,然后對運算結果做低通濾波,即可完成對中頻信號的下變頻操作。正交采樣模式下,兩路A/D轉換器提供正交輸入IIN及QIN,數字下變頻器的復乘法器輸出IOUT、QOUT為:

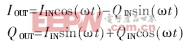

本振信號、復乘法器、低通濾波器均采用數字化設計。數字下變頻器采用ALTERA公司的APEX20K200RC240-1

器件。該器件典型門數為20萬,有豐富的邏輯單元和RAM單元,開發平臺Quartus II 自帶的宏模塊,如lpm_mult(乘法器宏模塊)、lpm_rom(ROM宏模塊)、lpm_add_sub(加法器宏模塊)等,給設計帶來了極大的方便。數字下變頻器原理圖如圖2所示。

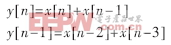

圖2中的數字表示相應模塊的數據寬度。濾波模塊是1個二階的低通濾波器,濾除混頻后的高頻分量。在一些專用的數字下變頻器件如STEL-2130中,濾波器的階數是可編程的,可以根據需要設置不同的階數,從而得到不同的濾波效果。考慮到FPGA的資源問題,設置濾波器的階數為固定的二階。濾波器輸入x[n]與輸出y[n]關系為:

該低通濾波器將相鄰的兩個輸入數據相加后作為輸出,即每兩個輸入數據對應一個輸出數據,輸入數據時鐘節拍為輸出數據時鐘節拍的2倍。

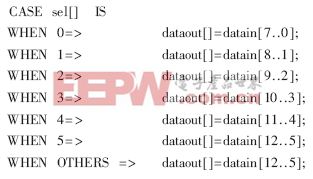

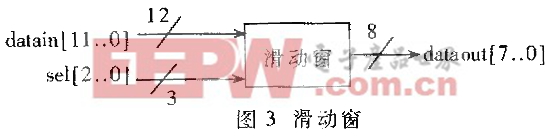

經過低通濾波后的數據經過滑動窗處理,滑動窗對輸入數據進行選擇輸出,用來動態調整相關峰的大小。在捕獲過程中觀察相關峰值時,通過調整滑動窗口,可以獲得不同幅度的相關峰值。選擇控制端由DSP寫控制字來決定,結構如圖3所示。滑動窗控制邏輯關系為:

符號擴展是為了與后面的相關累加器數據寬度保持一致,符號位擴展時需與輸入數據最高位的符號保持一致。

評論