10~37 GHz CMOS四分頻器的設計

1 引言

隨著通信技術的迅猛發展,人們對通信系統中單元電路的研究也越來越多。而分頻器廣泛應用于光纖通信和射頻通信系統中,因此,高速分頻器的研究也日益受到關注。分頻器按實現方式可分為模擬和數字兩種。模擬分頻器可由注入鎖定等結構實現,一般具有工作頻率高、功耗低等優點,但是分頻范圍較小,芯片面積較大。數字分頻器基于觸發器結構,一般分頻范圍較寬,芯片面積較小,但相對于模擬分頻器其工作頻率較低,功耗較大。這里采用UMC 0.13 um的CMOS工藝(其特征頻率fT約100 GHz),在電源電壓為1.2 V時,實現一個高速、寬分頻范圍的數字四分頻器。

2 電路設計

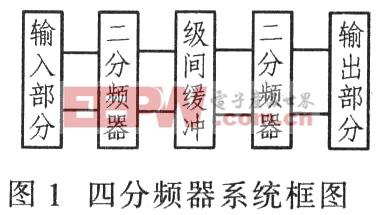

圖1為四分頻器的系統框圖。它由兩個二分頻器級聯而成。為了實現級間隔離和電平匹配,在兩個二分頻器之間加入級間緩沖電路。為便于區分這兩個分頻器,將前一個二分頻器稱為高速二分頻器,后一個二分頻器稱為低速二分頻器。因為要測試電路,需考慮輸入和輸出端口的阻抗匹配。為解決這些問題,電路中設計輸人和輸出部分。輸入部分除實現輸入阻抗匹配外,還要提供直流偏置。輸出部分用以保證測試時的阻抗匹配以及得到一定的輸出信號幅度。

2.1 二分頻器

這里采用的二分頻器為全差分的共柵動態負載結構,其框圖和電路圖如圖2a和圖2b所示。

分頻器相關文章:分頻器原理

評論