多路串行LVDS信號轉(zhuǎn)發(fā)電路 的設(shè)計(jì)與實(shí)現(xiàn)

O 引言

現(xiàn)代雷達(dá)和通訊系統(tǒng)中的電磁環(huán)境越來越復(fù)雜。為了保證系統(tǒng)控制命令的準(zhǔn)確下發(fā),提高控制信號的抗干擾能力,并兼顧降低系統(tǒng)功耗,可采用串行LVDS信號格式來設(shè)計(jì)轉(zhuǎn)發(fā)電路。

1 終端處理系統(tǒng)的構(gòu)成

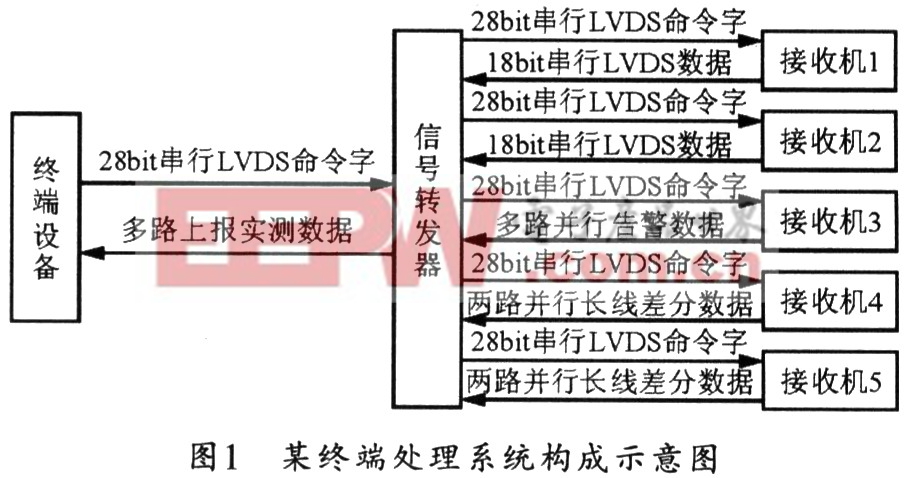

某終端處理系統(tǒng)需對前級五臺接收機(jī)實(shí)施工作狀態(tài)的控制。終端設(shè)備控制命令字是采用28bit串行LVDS信號發(fā)射的,五臺接收機(jī)收到控制命令字后各自對命令進(jìn)行譯碼,然后再執(zhí)行相應(yīng)的動作。錯(cuò)誤的動作會導(dǎo)致接收機(jī)上報(bào)終端設(shè)備的實(shí)測數(shù)據(jù)出錯(cuò),因而在終端設(shè)備和五臺接收機(jī)之間有一臺信號轉(zhuǎn)發(fā)器,以用于將終端設(shè)備的控制命令字轉(zhuǎn)發(fā)給五臺接收機(jī),同時(shí)將接收機(jī)上報(bào)的實(shí)測數(shù)據(jù)(也是串行LVDS信號格式)轉(zhuǎn)發(fā)給由終端處理機(jī)、終端錄取機(jī)和顯控計(jì)算機(jī)等組成的終端設(shè)備,其系統(tǒng)構(gòu)成如圖1所示。

由于進(jìn)出信號轉(zhuǎn)發(fā)器的信號類型較多,而且電源分機(jī)的+28V、±12V、±5V供電也要經(jīng)信號轉(zhuǎn)發(fā)器供給其它接收機(jī),因此,信號轉(zhuǎn)發(fā)器內(nèi)部的電磁環(huán)境非常復(fù)雜。本文主要介紹終端設(shè)備控制命令字的下發(fā)通路,即對信號轉(zhuǎn)發(fā)器中28 bit串行LVDS命令字轉(zhuǎn)發(fā)電路的設(shè)計(jì)加以論述。

2 芯片選擇

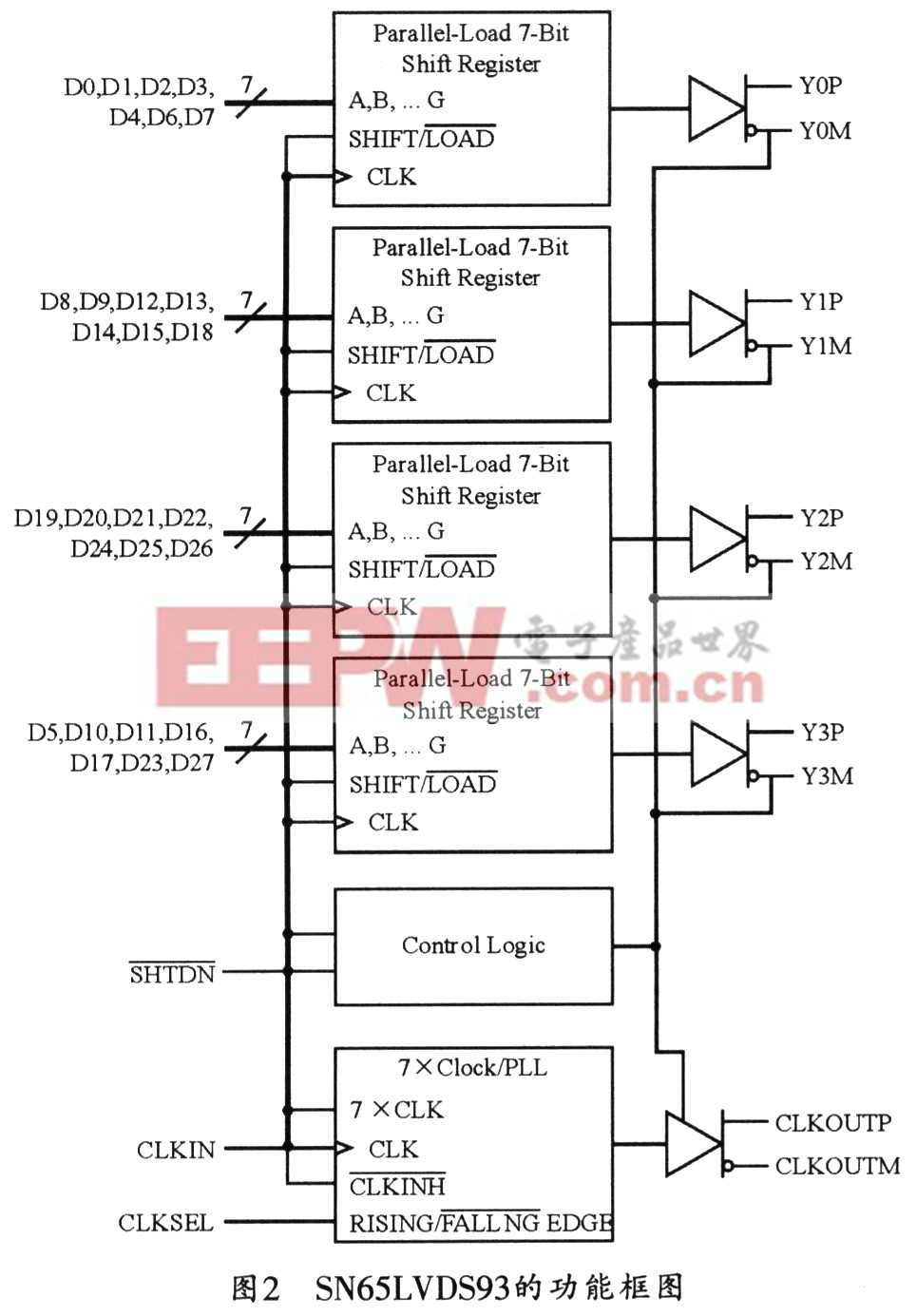

終端設(shè)備控制命令字可由SN65LVDS93芯片將28 bit并行格式轉(zhuǎn)變?yōu)?8 bit串行LVDS格式向外發(fā)射。該芯片可將28 bit數(shù)據(jù)分為四組,每組7 bit串行LVDS信號,再加上一組7倍于并行數(shù)據(jù)時(shí)鐘的LVDS時(shí)鐘信號,共有五組LVDS信號。圖2所示是SN65LVDS93芯片的功能框圖。該終端處理系統(tǒng)約定的系統(tǒng)時(shí)鐘是20 MHz,因此,7 bit串行LVDS信號的傳輸率是7x20=140 Mbps。而要把每組LVDS串行信號一分五分發(fā)到五臺接收機(jī),且接收端每臺接收機(jī)收到的五組LVDS串行信號在時(shí)序上要保持一致,即每組時(shí)序都如圖3所示。這樣才能保證五臺接收機(jī)收到的命令在時(shí)間軸上是一致的,從而保證命令碼中的控制動作一致。

DIY機(jī)械鍵盤相關(guān)社區(qū):機(jī)械鍵盤DIY

評論