基于MPSoC的以太網接口設計與實現

3 實驗結果

該硬件結構在Xilinx M525開發板上驗證實現,FPGA芯片型號為Virtex-5 XC6VLX550T,其中芯片邏輯資源為207360,存儲資源為11.39 MB,寄存器資源為207 360,系統硬件在FPGA中資源占用如表1所示。本文引用地址:http://www.j9360.com/article/155185.htm

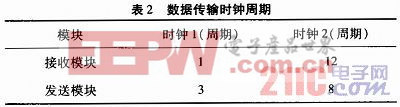

表1是系統設計通過ModelSim功能仿真后,在Xilinx ISE工具上綜合后的結果,綜合頻率高達245.562 MHz。在系統運行中,以太網控制器IP核時鐘工作頻率在125MHz,系統時鐘頻率為100MHz。通過仿真和FPGA下載驗證后,接口通訊時鐘周期統計如表2所示。

通過表2可以看出,以太網接口設計在完成兩種協議轉換和跨時鐘數據傳輸中,通訊響應時間短,且具有實時和穩定傳輸,避免了異步時鐘在數據傳輸中的效率問題。

實驗測試,把FPGA開發板與PC機通過網線連接,如圖6所示。在PC機上編寫軟件程序,用于發送和接收硬件系統數據,通過修改數據文件,測試不同深度的數據傳輸。比較發送數據和接收數據文件,判斷傳輸誤碼率。

實驗測試了不同文件大小的數據傳輸需要時間,統計結果如圖7所示。測試結果,發送與接收文件數據,與預期結果一致。通訊時間與數據文件大小近似于線性關系,且傳輸時間短。以太網接口設計模塊為MPSoC承擔網絡數據通訊,提供了實時和高吞吐率的通訊速度。此外,以太網模塊可以用于系統單模塊集成調試傳輸源數據,提高驗證效率。以太網接口模塊也可以應用于通訊網絡,實現系統數據與網絡通訊信息的交換。

4 結束語

研究了以太網在MPSoC中的數據通訊,解決了系統在網路通訊中的實時和高吞吐率的數據傳輸瓶頸。通過該接口與多核系統通訊,可以完成局域網到廣域網數據信息傳遞。

評論