聲納信號處理中UDP協議數據傳輸研究與設計

摘要:為了在聲納系統中通過以太網口進行大批量、高速率的數據傳輸處理,在FPGA中硬件實現了嵌入式UDP協議棧,完成了架構設計、軟件仿真驗證及硬件實現。用FPGA硬件實現UDP協議棧,加速了網絡數據處理能力,使信號傳輸速率達到了80MB/s,實現了千兆級通信,很好地提高了聲納系統中數據傳輸速率和系統性能。同時,用FPGA硬件實現UDP協議,棧減小了PCB版圖面積和布局布線復雜度,提高了開發效率,有效地降低了開發成本。

關鍵詞:UDP協議;FPGA;數據傳輸;信號處理

0 引言

UDP協議是一個簡單的面向數據報的傳輸層協議,提供不呵靠的傳輸層服務。它只負責將應用數據打包交給網絡層,但是不保證數據報能正確到達。UDP協議提供了一種最簡單的基于數據包的、不可靠的傳輸機制。其特點是以數據包為最小傳輸單位,并且沒有任何流量控制機制,適合傳輸效率要求較高且對傳輸可靠性要求不高的情況。

現有XXX型號聲納系統需要實現Link口轉UDP格式數據傳輸,以滿足大批量、高速率的數據傳輸要求,現有的CPU和軟件協議棧無法滿足此要求。經仔細研究,發現用FPGA硬件實現UDP協議棧,可以很好地提高數據傳輸速率,滿足該聲納系統的性能要求。本文實現了一種可配置、可重用的硬件UDP協議棧,完成了UDP協議的FPGA設計:設計了UDP發送端模塊,UDP接收端模塊以及Link端模塊等,同時對所設計系統進行了驗證。經過實際驗證,系統數據通信速率達到了80 MB/s,實現了千兆級以太網通信,很好地提高了聲納系統中數據傳輸速率和系統的性能,滿足了XXX型聲納系統對大批量、高速率數據傳輸的要求。并且,此方案減小了PCB版圖面積和布局布線復雜度,可以移植到任何其他的FPGA設計中,使開發效率得到了極大的提高,有效地降低了開發成本。

1 聲納系統信號處理中UDP協議的FPGA設計

1.1 UDP模塊設計

UDP包頭包括IP,端口號,UDP包長度,CHECKSUM四個部分。并且UDP信息包的標題很短(標題即頭部),只有8 B,其中,源端口(2 B)、目的端口(2 B)、長度(2 B)、校驗碼(2 B)。這里設計的架構通過發送端對數據進行打包,通過接收端進行解包。

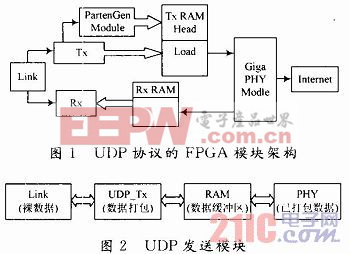

UDP協議的FPGA架構如圖1所示。

發送端(Tx)是頭信息生成模塊,從Link口發出的數據傳入發送模塊Tx內。然后,發送模塊Tx中的裸數據發送到數據緩沖區RAM中,經由PartenGen模塊在數據前面添加首部,即為數據進行傳輸層協議UDP打包。傳輸層協議打包好的數據傳輸到物理層模塊,通過物理層調節芯片傳送到以太網口。發送完成后,發送模塊恢復空閑狀態,等待下一次數據發送。在發送過程中,傳輸數據的IP地址是固定的。UDP發送過程沒

有可靠性的保證機制,只是進行數據的打包傳輸。發送模塊結構圖如圖2所示。

評論