CDMR數字對講機設計

摘要:提出了一種基于DMR標準的零中頻CDMR數字對講機硬件射頻電路的實現方法,采用圖文結合的方式表達設計思路。給出了CDMR關鍵技術的解決思路以及實現方法,完成了原理圖以及PCB的設計。實驗測試結果表明設計滿足DMR標準。

關鍵詞:CDMR,零中頻,數字對講機,硬件射頻電路

0 引言

工信部2009年666號文件《工業和信息化部關于150MHz 400MHz頻段專用對講機頻率規劃和使用管理有關事宜的通知》的頒發吹響了數字對講機發展的沖鋒號,DMR數字技術即成為中國對講機”模轉數”進程中企業選擇的標準之一,DMR制式的數字對講機已亮相市場,并得到較好的評價。自2011年1月1日起,停止對該頻段內模擬對講機設備型號的核準,到2016年該頻段全面停止模擬對講機使用。目前數字對講機的標準不統一、成本高、互通性差成制約數字對講機發展的瓶頸。目前數字對講機市場上存在多種數字技術標準,其中最受關注的是DMR、DPMR和PDT,而制造商對DMR的興趣尤為突出。清華大學無線與移動通信技術研究中心、北京交通大學、摩托羅拉系統(中國)有限公司等13家單位聯手發起了專業數字無線通信技術CDMR論壇,并于2011年9月1日在杭州舉辦了第一屆CDMR研討會,至今已吸收成員40家。CDMR聯盟的樣機于2012年12月通過國家無線電管理局的型號核準,并于2012年12月18日6家聯盟成員完成了互通測試。本文介紹的對講機設計就是基于CDMR聯盟的數字對講機設計與實現方法,該設計成本低、互通性強、易于生產,受到了廠商的好評。

1 數字對講機的原理

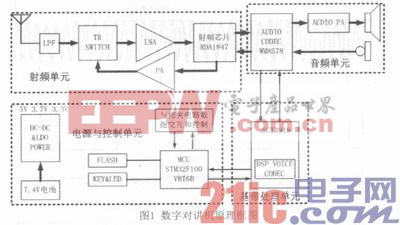

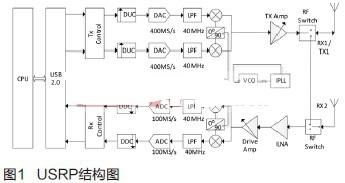

CDMR數字對講機主要由電源與控制單元、基帶處理單元、音頻單元、射頻單元組成。其原理框圖如圖1所示。

1.1 電源與控制單元

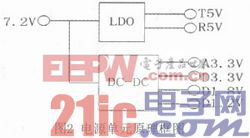

電源單元把7.2V電池電壓轉換成CDMR數字對講機收發所需的5V電壓,選用了帶使能端的LDO,便于MCU對電源的控制。MCU以及基帶處理需要3.3V、1.8V、1.2V電壓,為了提高電源的效率,利用開關電源IC首先轉換成3.7V電壓,再利用LDO轉換成3.3V、1.8V、1.2V電壓。為了避免開關電源的開關頻率對RF的影響,在電路設計以及PCB設計上進行了特殊處理,做到了提高了電源效率,射頻頻譜的純凈。

控制單元主要由MCU STM32F100完成,該MCU的性價比高、功耗低、功能強大。MCU完成對收發信機的收發切換控制、TDMA時序控制、信道切換控制以及對基帶處理單元的初始化。

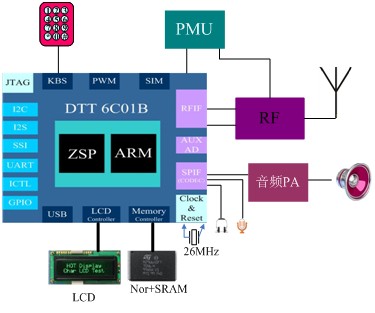

1.2 基帶處理單元

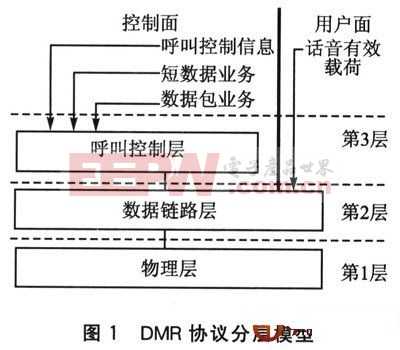

基帶處理單元主要完成數字話音的編解碼、語音壓縮、信道編解碼等。基帶處理采用SCT3918,該芯片支持DMR Tier 1,支持收發時隙模式和連續模式,支持DMR協議的物理層、數據鏈路層以及呼叫控制層協議,支持自動同步檢測和調制指數可編程,支持兩點調制和IQ調制,在12.5kHz的信道帶寬內速率高達9600bps。該芯片還植入了清華大學的ASELP的語音處理算法并且能加密、也植入了AMBE+2和AMBE+2C的語音算法。該芯片還支持模擬話音模式,內部自帶加重和去加重、語音濾波等處理,支持CTC;SS和DCS。

1.3 音頻單元

音頻單元主要完成語音的模數和數模轉換以及音頻放大、MIC的放大與預處理。MIC信號首先經過由運放組成的有源濾波器濾波,然后分成兩路,一路用于VOX信號檢測,另一路經過模數轉換后送給基帶處理單元進一步處理后發射。CDMR接收的信號經過基帶處理單元解碼并數模轉換后,經過音頻放大器推動SPK播放語音。音頻放大器采用差分放大器,有效地降低了干擾,提高了音質。

評論