基于DSP的高速數據采集與處理系統

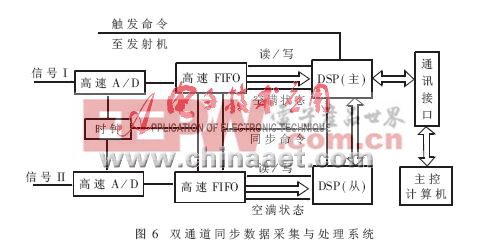

本文設計并實現了一種基于DSP的高速數據采集與處理系統。該設計方案電路簡單、可靠性好、具有一定的通用性、可以進行多通道擴展。系統主要包括高速A/D、高速緩存、DSP處理器、通訊接口四個部分,其結構示意圖如圖1所示。

本文引用地址:http://www.j9360.com/article/152629.htm1 同步與過程控制

在通常的數據采集系統中,測量過程是通過對A/D變換器的控制來實現的。但對于一個高速采集系統而言,這種方法有局限性。因為高速A/D建立穩定的工作狀態需要相當長時間,頻繁的改變A/D的工作狀態會影響測量的精度,嚴重時會造成信號的失真。

在本設計方案中,同步命令并不直接作用于高速A/D。自通電時起,A/D和時鐘電路始終處于工作狀態,同步命令通過對高速FIFO的寫入端的控制,即允許或禁止對FIFO寫入,實現對采樣數據的取舍。與A/D相比,高速FIFO的寫有效時間為3ns,對同步和過程控制更為有利。

一次完整的測量過程是從DSP發出同步命令開始的。同步命令一方面觸發發射機工作,另一方面允許對FIFO寫入,對采樣的數據進行存儲。當存儲的數據到達預定的數量時,FIFO的特定狀態位置位,引發DSP外部中斷。在中斷服務程序中,DSP禁止對FIFO寫入、中斷數據的存儲,同時復位該狀態位。然后讀取數據,待完成數據處理過程之后,DSP對FIFO復位清零。此即完成一次測量。

2 高速A/D轉換器

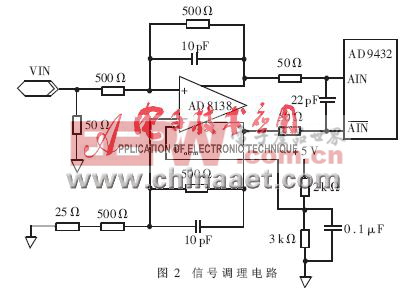

高速A/D轉換器選用AD9432,采樣位數12位,最高采樣速率105MHz,模擬帶寬500MHz,差分信號輸入,差分外部時鐘,片內帶有輸入緩存和采樣/保持器,12位并行數據輸出,52引腳LQFP封裝。

由于AD9432要求差分輸入形式,因此對于單端輸入信號必須經過圖2所示的信號調理電路變換為差分形式。圖中,AD8138為差分輸出的高精度運算放大器。

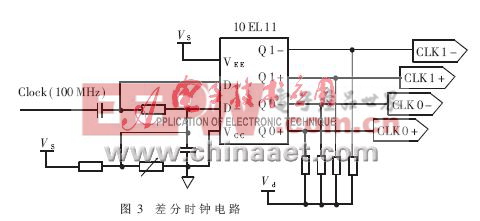

時鐘對于一個高速數據采集系統而言是十分重要的。在最高采樣頻率下,為了保證測量的精度,AD9432要求時鐘波形的上升沿和下降沿小于2ns,這樣的標準在TTL邏輯下難以實現,但利用ECL器件可以有效地解決此問題,圖3為差分時鐘電路。

需要說明的是:ECL器件的驅動能力有限,一路差分時鐘輸出一般只供一個器件使用。

3 高速緩存FIFO

高速緩存是系統中的一個關鍵環節,根據系統的需求我們選用CY7C4245。

CY7C4245是高速、低功耗4K×18 FIFO存儲器,讀寫周期為10ns,具有獨立的18位輸入、輸出接口和讀、寫時鐘信號,可以實現同步讀寫操作。CY7C4245提供五種狀態指示:Empty、Almost Empty、Half Full、Almost Full、Full,分別代表當前數據存儲的深度。其中Almost Empty 和Almost Full 為可編程空滿狀態位,可根據系統的需求對存儲進行設定。FIFO的狀態信息代表了已采樣的點數,當采樣點數達到預期的數量時,相應的狀態位置位,觸發DSP的外部中斷,中止測量過程,由 DSP讀取數據進行處理。

4 DSP處理器

4.1 TMS320F206的特點

DSP是整個采集系統的核心,本文中選用 TMS320F206。該產品屬于TI公司采用CMOS集成電路技術生產的TMS320C2XX系列,設計結構及其匯編指令集與TMS320C5X相兼容,其主要特點如下:

(1)運算速度可以達到40MIPS;

(2)4.5K片內RAM和32K片內FLASH存儲器;

(3)32位算術邏輯單元和32位累加器;

(4)16位地址總線和16位數據總線;

(5)具有一個異步串行通訊接口和一個同步串行通訊接口,異步串行口具有波特率自動檢測功能;

(6)價格低廉。

4.2 數字信號處理

數字信號處理是DSP應用的主要方面。DSP所提供的數學運算能力和運算速度遠遠高于單片機,具有更為豐富的指令集和更大的內存空間,可以實現較為復雜的數學算法。

DSP首先要完成數制轉換,AD9432的量程為-500mV~+500mV。對于負電平,采樣數據以二進制補碼的形式輸出,需將12位補碼轉換為16位二進制整數;更為重要的是DSP要實現系統所要求的數字信號處理算法,如快速維納濾波、FFT等。

5 數據通訊

5.1 異步串行通訊

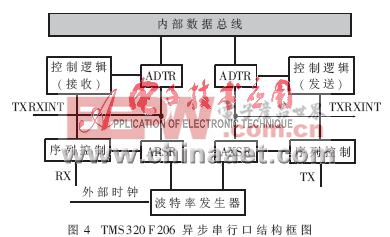

數據采集系統與主控計算機之間的數據交換采用異步串行通訊方式。TMS320F206帶有一個異步串行通訊端口,在40MHz外頻條件下,最高傳輸速率達到2.5Mbit/s。發送和接收使用獨立的緩沖區,可以實現全雙工工作方式,異步串行口的工作框圖如圖4所示。

其中,AXSR為異步串行發送移位寄存器;ARSR為異步串行接收移位寄存器;ADTR為異步數據發送接收寄存器,TXRXINT為發送接收中斷(硬件中斷)。

此外,TMS320F206有一個同步串行口,用于多機并行工作方式下DSP之間的數據交換。在40MHz外頻時,其最高傳輸速率為20Mbit/s。

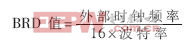

5.2 波特率設置

TMS320F206有一個16位寄存器BRD用于設定異步串行通訊所使用的波特率,其數值計算公式如下:

表1列出了不同外部時鐘頻率下常用波特率對應的BRD數值。

5.3 串行通信軟件設計

為了提高效率,數據的發送和接收均采用中斷方式,串行通訊波特率為57600,匯編程序代碼如下:

串行口初始化:

setc INTM ;禁止所有中斷

splk #0ffffh, ifr ;清中斷

splk #0000h, 60h

out 60h, wsgr ;清等待狀態

splk #0c180h, 61h

out 61h, aspcr ;復位異步串口,設發送、接收

中斷,一個停止位

splk #0e180h, 61h

out 61h, aspcr ;配置異步串口

splk #4fffh,62h

out 62h,iosr ;復位異步串口各狀態標志

splk #002Bh, 63h

out 63h, brd ;設波特率為57600

splk #020h, imr ;允許異步串行中斷

mar *, ar1

lar ar1, #rxbuf ;設緩沖區指針

mar *,ar0

lar ar0, #size ;設緩沖區大小

發送中斷服務程序:

..........

splk #0ffffh, ifr ;關中斷

out *+, adtr ;發送數據

mar *,ar0 ;發送計數

banz skip, ar1 ;若仍有數據,發送

緩沖區指針加1

skip: splk #0020h, ifr ;允許中斷

clrc INTM ;清中斷

ret

接收中斷服務子程序:

............

splk #0ffffh, ifr ;關中斷

in 68h,iosr

bit 68h,7

bcnd skip,ntc ;檢測接收標志位

in *, adtr ;讀數據

mar *,ar0

banz skip, ar1 ;接收數據計數

............

skip: splk #0020h,ifr ;開中斷

clrc INTM

ret

其中ifr為中斷標志寄存器;aspcr為異步串行口控制寄存器;imr為中斷屏蔽寄存器;iosr為I/O狀態寄存器;wsgr為等待狀態寄存器。

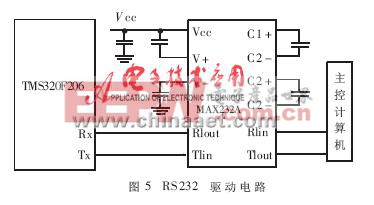

6 RS232接口電路

該系統中DSP與主控計算機的數據通訊采用RS232標準,驅動電路選用MAX232A芯片。MAX232A功耗低、集成度高、片內集成電荷泵,只需外接+5V電源,具有兩個發送接收通道,接口電路簡單、可靠性好。RS232驅動電路如圖5所示。

7 系統的擴展

本設計方案電路簡單、易于實現、具有一定的通用性,在此基礎上可以擴展為同步采樣的多通道采集系統,如圖6所示。圖中,主從DSP之間的數據通訊采用同步串行方式。

需要注意的是:對于多通道同步采樣系統,應盡可能地保證各通道參數的一致性。

根據本文內容設計并實現的雙通道同步數據采集與處理系統已成功應用于分布式光纖測量系統,取得了很好的效果,實踐證明本文的設計是可行有效的。

評論