基于OMAP5912的語音采集系統的設計與實現

0 引 言

近年來,高速發展的語音信號處理技術已在音頻信息的處理、傳輸和存儲等方面得到廣泛應用。同時,隨著高性能數字信號處理器(Digital Signal Processor,DSP)的日益普及,利用DSP對語音信號處理進行算法研究和實時實現正成為新的熱點。在此設計并實現了一種語音采集系統。該系統為語音信號處理的算法研究和實時實現提供一個通用平臺。同時,與已有的聲卡等具有語音采集功能的設備相比,該系統具有結構簡單,效率高,便于攜帶等特點,因此也可以作為便攜式設備或手持終端的一部分進一步加以開發和應用。

1 芯片簡介

OMAP5912采用獨特的雙核結構,內含1個實現控制功能的帶有TI增強型ARM926EJ―S(簡稱ARM9)內核的處理器和1個實現數據處理功能的高性能、低功耗TMS320C55x DSP(簡稱DSP)內核。ARM9處理器可用來實現各種通信協議、控制和人機接口;DSP具有多條數據地址總線,非常適合數據密集的多媒體處理,并具有極低的功耗。

TLV320AIC23(簡稱AIC23)是TI推出的一款高性能的立體聲音頻Codec芯片,內置耳機輸出放大器,支持MIC和LINE IN兩種輸入方式(二選一),且對輸入和輸出都具有可編程增益調節。AIC23的模數轉換(ADCs)和數模轉換(DACs)部件高度集成在芯片內部,采用了先進的Sigma―delta過采樣技術,可以在8~96 kHz的頻率范圍內提供16 b,20 b,24 b和32 b的采樣,ADC和DAC的輸出信噪比分別可以達到90 dB和100 dB。與此同時,AIC23還具有很低的能耗,回放模式下功率僅為23 mW,省電模式下更是小于15μW。

2 系統的硬件設計

2.1 系統的硬件結構

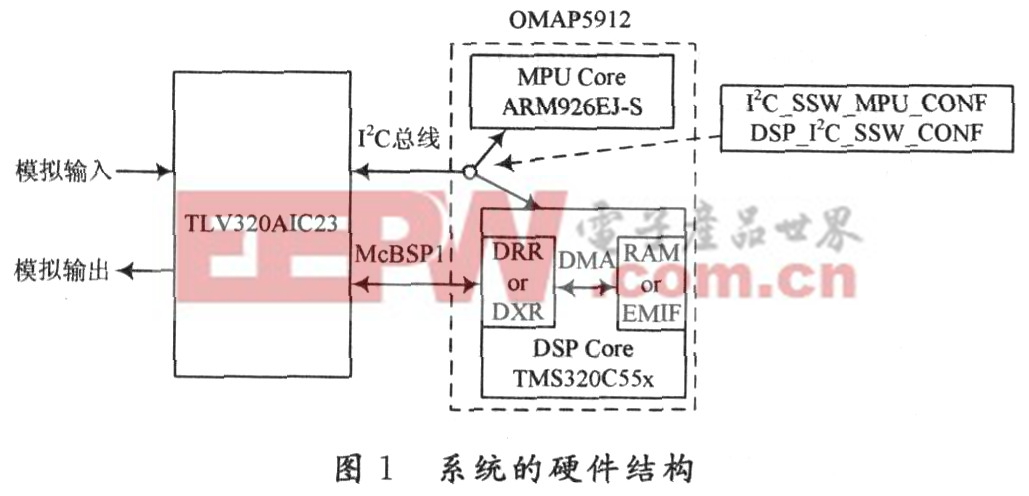

語音采集系統主要包括兩個模塊:以AIC23為核心的語音采集模塊;以OMAP5912的DSP為核心的語音數據接收處理模塊。

為使AIC23正常工作在需要的狀態下,必須通過I2C總線對其進行配置。AIC23采集的語音信號經過A/D轉換后,通過McBSPl傳送到接收寄存器DRR,然后經DMA通道傳送至接收緩沖區。存放在發送緩沖區的數據,通過DMA通道傳送到McBSPl的發送寄存器DXR,然后傳送至AIC23,經過D/A轉換后,由HEADPHONE輸出,如圖1所示。

2.2 系統的硬件接口設計

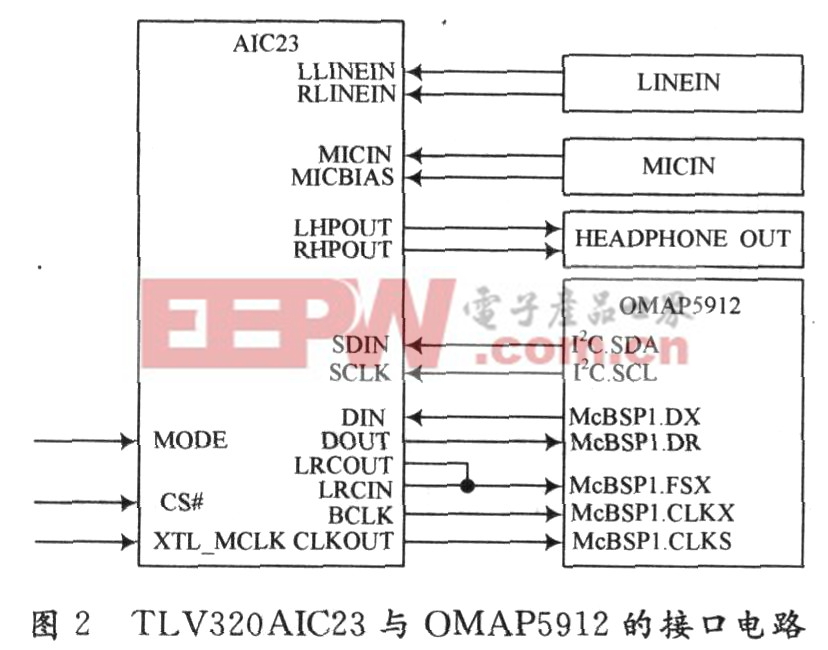

利用OMAP5912的I2C總線和McBSPl完成對AIC23的控制和通信。I2C總線與AIC23的控制口相連,McBSPl與AIC23的數據口相連。AIC23設置為Master模式,向McBSPl提供時鐘和幀同步信號。McBSPl.DX作為AIC23的輸入通道,McBSPl.DR作為AIC23的輸出通道,如圖2所示。

3 系統的軟件設計

系統的軟件分兩個方面來說明:主程序和中斷服務程序。

3.1 主程序

評論