DSP的SPI口和串行EEPROM在變頻器中的應用

器件的存儲器部分是帶有XICOR公司的塊鎖存保護的CMOS串行EEPROM 陣列,陣列的內部組織是x8位。具有串行外圍接口(SPI)和軟件協議的特點,允許在簡單的四線總線上工作。利用XICOR專有的直接寫入晶片,提供最小為100,000次擦寫和最少為100 年的數據保存期。

4.1硬件設計

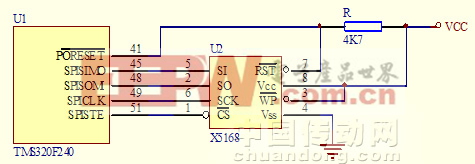

圖1 TMS320F240與X5168連接原理圖

串行外設接口(SPI)有兩種工作模式:主模式和從模式,與X5168 連接時工作于主模式。從圖中可看到,X5168通過四根線來完成與DSP的數據交換,DSP的SPISIMO、SPISOMI、SPICLK、SPISTE引腳分別連接X5168的SI(串行輸入)、SO(串行輸出)、SCK(串行時鐘)、/CS(片選端),此時的F240控制器稱為“主機”,這種情況下,SPI在SPICLK引腳上提供了整個串行通信網絡所需的串行時鐘;數據從SPISIMO引腳輸出;并鎖存從SPISOMI引腳輸入的數據;SPIBRR寄存器決定了整個串行通信網絡中數據發送和接收時的位傳輸率。

寫入SPIDAT的數據啟動了SPISIMO引腳上的數據發送,先發送最高有效位;同時,接收的數據通過SPISOMI引腳移入SPIDAT的最低有效位。當有一定數量的數據位通過SPIDAT移位時,產生下列事件:

一、SPI INT FLAG置1

二、SPIDAT的內容傳送到SPIBUF

三、如果SPI INT ENA也被置1,則產生中斷請求

在主模式中,無論寄存器SPIPC1的位5(SPISTE FUNCTION)為何值,SPISTE引腳都將用作通用數字I/O引腳。在本設計中,引腳SPISTE用作從機SPI模塊的片選引腳;在將主機數據傳送到從機器件之前,應將從機器件片選引腳拉低電平,并且在傳送完主機數據之后,重新將該引腳拉為高電平。

4.2軟件設計

4.2.1 TMS320 F240的SPI初始化

上文介紹了F240的SPI模塊的功能,配置寄存器串行外設接口工作于主模式,波特率設置為2MHz,初始化程序如下:

void SPIinitial(void)

{ *SPICCR=0xc7; //復位SPI

*SPICTL=0x06; //主模式,使能TALK,禁止SPI中斷

*SPISTS=0x00; //清中斷標志

*SPIBRR=0x04; //波特率設為SPICLK=SYSCLK/4+1=2MHz,SYSCLK=10MHz

*SPIPC1=0x52; //SPISTE引腳配置成輸出引腳,SPICLK被配置成串行時鐘的輸

//入或輸出

*SPIPC2=0x22; //SPISIMO,SPISOMI用作SPI輸入輸出

*SPICCR=0x47; //上升沿發送,下降沿輸入數據鎖存,無時延,字符長度為8

}

4.2.2 F240對X5168的讀寫程序

評論