基于ARM的胎兒心電信號數據采集系統

3.2 A/D采集與控制

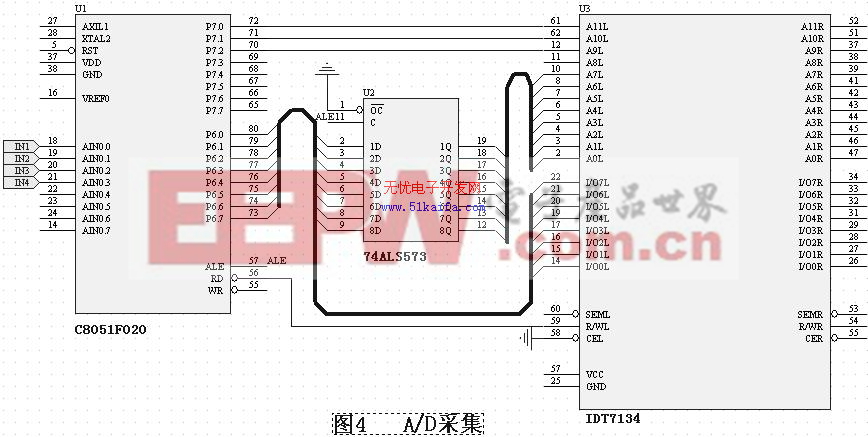

考慮到胎兒心電信號數據采集量很大,實時性要求高,同時為了保證數據流動的連續性,系統專門設置C8051F020片上系統為核心的數據采集模塊,通過一雙端口RAM,將采集來的數據傳送到嵌入式主控處理器,該主控處理器對整個系統協調管理和控制,主要完成系統的設置、指揮指令的下達、系統工作狀態的監測,數據保存等。采用C8051F020特點如下:運算速度快;片內集成了多通道12位和8位A/D轉換器,采樣速率100 ksps;具有64 K B的Flash存儲器,4KB內部數據RAM以及外部64 KB數據存儲器接口等。雙端口RAM采用的是IDT公司的先進先出(FIFO)存貯器芯片IDT7134芯片,緩存容量為8KB,接口方便,結構如圖4所示。

整個目標平臺以S3C44B0X處理器為核心,由于數據量大,本系統擴展了容量為2MByte Flash器件SST39VF160,用來下載啟動系統及對系統進行初始化的程序BIOS,嵌入式操作系統µ;C/OS-Ⅱ,圖形界面系統µ;C/GUI及應用程序,Flash ROM映射在S3C44B0X的Bank 0上;系統上電時處理器從Flash ROM的0x0000000地址處取指令開始運行[1] ;64MByte SDRAM芯片HY57V641620HG,系統啟動后BIOS把應用程序搬移到SDRAM中運行,SDRAM還開辟出一部分充當LCD顯示緩沖區(顯存),其余部分用來存儲臨時數據、堆棧等,SDRAM映射在S3C44B0X的Bank 6上,也就是OxC000000地址處;320×240彩色LCD顯示屏,提供良好的人機交互界面,由S3C44B0X自帶的LCD控制器驅動;4×4鍵盤,對整個終端進行操作和控制。

4 系統軟件設計

軟件設計主要包括:µ;C/OS-Ⅱ在S3C44B0X上的移植,胎兒心電數數據采集和存儲,LCD顯示以及鍵盤程序。本系統采用可重入代碼編譯器EmbestIDE Pro for ARM。

評論