基于CPCI總線多DSP系統的高速主機接口設計

在現代通信、雷達和聲納系統中,隨著實時處理要求的不斷提高,對數字信號處理系統也提出了更高的要求。板載多片高性能的DSP芯片,配合大容量的SDRAM,可以很好地滿足上述要求,并且已經成為了數字信號處理系統發展的趨勢。采用CPCI總線集成系統,可以方便主機進行調試,控制和管理DSP系統。系統中的主機接口可以使主機通過CPCI總線訪問板上的DSP和SDRAM芯片,這是多DSP系統設計的關鍵點之一。

本文引用地址:http://www.j9360.com/article/152127.htm不同于以往簡單地使用一個CPLD進行粘合邏輯設計,本文提出了一種基于雙狀態機+Cache,預存預取的主機接口設計結構。在主機接口中設立了一個Cache,降低了CPCI總線與板上DSP和SDRAM芯片的耦合度,并且設計了兩個獨立狀態機分別進行控制。這顯著提高了主機訪問DSP和SDRAM的速度,為DSP系統的應用提供了更廣闊的平臺。本文詳細闡述了如何完成CPCI總線和DSP、SDRAM芯片間的數據傳輸,分析了設計難點,并給出了邏輯框圖。

1 系統設計方案

圖1是系統設計框

圖,系統采用PLX公司的PCI9656接口芯片,它可以很方便地將時序相對復雜的PCI協議轉化為相對簡單的局部端訪問協議。在基本不損失性能的同時,簡化了邏輯設計要求,使開發者可以更為關注后端數據接口問題。

FPGA采用Xilinx公司的X2V1000它有近100萬門的邏輯資源和720KB的BlockRAM可以靈活搭建控制邏輯和Cache緩存 DSP采用ADI公司的… src=Image/20090601155734566221_new.jpg>

FPGA采用Xilinx公司的X2V1000,它有近100萬門的邏輯資源和720KB的BlockRAM,可以靈活搭建控制邏輯和Cache緩存。

DSP采用ADI公司的ADSP-TS201S,共有4片,工作頻率是600MHz,總共可以提供14.4GFLOPS的運算能力[1]。

SDRAM采用Hynix公司的HY57V561620C,容量共有128MB,可以基本滿足數據存儲的要求。

2 FPGA的接口設計

2.1 FPGA在系統中的作用

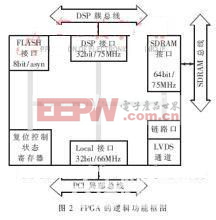

FPGA主要實現如下功能接口:(1)DSP接口。提供一個PCI Local總線到DSP共享總線的界面,完成兩套總線之間的邏輯仲裁及讀寫控制信號等;(2)SDRAM接口。提供一個PCI Local總線到SDRAM總線的界面;(3)FLASH接口;(4)鏈路口;(5)Register管理模塊。圖2給出了FPGA的各種接口與系統其他部分的關系圖。本文將重點討論主機和DSP、SDRAM間的訪問。

評論