基于NiosII處理器的通用AD IP核的設計與實現

Nios II是Altera公司開發的第二代可進行SOPC設計的RISC型處理器軟核,具有定制指令、硬件加速、可重配置、低成本和無與倫比的靈活性等特點[1]。基于NiosII處理器的通用AD IP核是一種全新的設計思路與實現方案,它可以將市面上任意一款AD芯片制作成IP核并集成到NiosII系統中使用,具有高性能、參數可配置、可移植、可裁剪等特點,并且具有很高的靈活性、實用性,從而更能滿足設計的要求。

本文提出了一種基于NiosII處理器的通用AD IP核來實現嵌入式數據采集系統的新方案,在Altera公司的FPGA芯片CycloneII EP2C35F484C8 上完成了硬件驗證,最終應用到某數據采集系統的設計中。

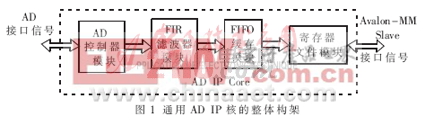

1 通用AD IP核的整體構架

通用AD IP核是針對所有AD芯片設計的,它可以將市面上任意一款AD芯片集成到NiosII系統中使用,其整體構架如圖1所示。

整個通用AD IP核主要由4個子模塊組成:AD 控制器模塊、FIR 濾波器模塊、FIFO 緩存模塊和帶Avalon-MM Slave接口的寄存器文件模塊。首先AD控制器控制AD芯片對外界的模擬信號的采集,采集到的數據送入FIR濾波器進行數字濾波,然后將經過數字信號處理后的數據存入FIFO緩存中,當FIFO緩存數據為滿時,會向NIOSII處理器產生一個中斷,頂層應用程序可以通過中斷服務程序將FIFO中的數據讀到內存中進行處理。帶Avalon-MM Slave接口的寄存器文件模塊提供了所設計的AD IP核的任務邏輯與Avalon交換結構交換信息的途徑。有了寄存器文件模塊,NiosII處理器就可以通過Avalon接口采用“基地址+地址偏移量”的方式來訪問AD IP核內部的各寄存器[2]。

2 AD IP核各個模塊的設計與實現

由于市面上AD芯片的種類和型號非常多,不可能在此一一進行闡述。本設計以一款常用的典型AD芯片TLC549為例,詳細闡述針對這款AD芯片的IP核的各個模塊的設計與實現。

2.1 AD控制器模塊的設計

本系統采用AD轉換芯片TLC549,它是TI公司生產的一種低價位、高性能的8位A/D轉換器,它能方便地采用三線串行接口方式與各種微處理器連接,構成各種廉價的測控應用系統[3]。

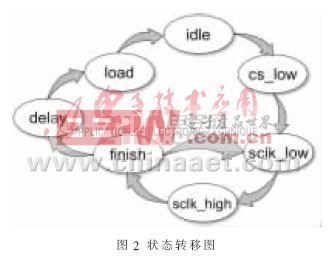

本文利用有限狀態機的方法采用Verilog HDL硬件描述語言設計了一個TLC549控制器,從而完成了對TLC549 AD芯片的時序控制,它的狀態轉移圖如圖2所示。

由圖2可以看出,狀態機一開始處于idle狀態。在下一個clk時鐘周期上升沿時刻進入cs_low狀態,在cs_low狀態將cs輸出引腳拉低并延時2 μs。當2 μs延時完成時,狀態機進入sclk_low狀態,在sclk_low狀態將sclk輸出引腳拉低并延時0.5 μs。當0.5 μs延時完成時,狀態機進入sclk_high狀態,在sclk_high狀態將sclk輸出引腳拉高并延時0.5 μs,同時讀取串行數據線miso上的AD采樣值并將其存入移位寄存器中。當0.5 μs延時完成時,進入finish狀態,在該狀態狀態機對已經接收到的串行數據位數進行判斷,如果小于8說明串行數據還沒有接收完畢,加1并進入sclk_low狀態;如果等于8說明8位AD采樣值已經接收完畢,進入delay狀態。在delay狀態將延時30μs,當30 μs延時完成時將進入load狀態。在load狀態,狀態機在data_ready輸出引腳上拉高一個clk時鐘周期并在data[7..0]引腳上輸出接收到的8位采樣數據。在下一個clk時鐘周期上升沿狀態機將自動進入idle狀態,以進行下一次AD數據采集。由此周而復始不斷循環從而完成通過TLC549 AD芯片實現對外界模擬信號的實時采集。

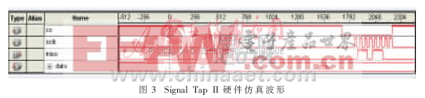

本文采用Quartus 軟件集成的Signal Tap II 嵌入式邏輯分析儀軟件對TLC549控制器模塊進行硬件仿真,波形如圖3所示。

由圖3可以看出,在cs、sclk和miso信號的時序配合下,data信號線上輸出穩定的8位AD采樣數據,經過數字量到模擬量的轉換發現與外界輸入模擬值一致,從而完成了TLC549控制器模塊的驗證。

AD控制器模塊是針對某一款具體的AD芯片而設計的,如果選用不同款式的AD芯片,則需要參考該芯片的芯片手冊設計針對該款AD芯片的AD 控制器模塊。

評論