基于SoPC的通用在線調試器設計

目前,國內生產的部分在線仿真調試器可以對部分嵌入式芯片進行仿真調試。但從本質上,這些仿真調試器無法對所有帶在線調試功能的嵌入式芯片進行仿真調試。BDI2000和TRACE32等仿真器可以在不改變硬件條件下,通過下載針對特定嵌入式芯片的調試“核”來實現對不同嵌入式芯片的仿真調試,但是非常昂貴,難以適應國內絕大多數中小企業的實際需求。

本文基于SOPC軟硬件協調設計驗證技術設計了一款通用在線調試器。SOPC技術將傳統的在線調試器以芯片形式呈現,采用知識產權核(IP core)復用技術,抽象各種不同架構的嵌入式處理器接口,給出支持統一調試接口的IP core架構,提出了基于通用在線調試器的嵌入式軟件調試方法。

本文介紹了系統架構,以及關鍵子系統的工作原理及其與所處硬件環境之間的交互,最后對JTAG IP core子系統進行了仿真驗證。

1 整體設計

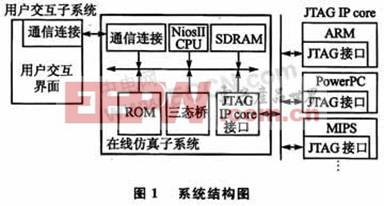

系統由用戶交互、在線仿真和JTAG IP core三個子系統構成,如圖1所示。

用戶交互子系統包括TCP/IP通信端口與用戶交互界面。它主要負責訪問和處理源文件;接收調試命令,根據TCP/IP協議封裝成調試命令請求包,發送給通用調試器;同時,解析目標機的響應。其中,通信端口負責與通用在線調試器通信。

在線仿真子系統是一個針對不同類型嵌入式處理芯片的高擴展性嵌入式系統。它包括硬件部分和軟件部分。硬件部分采用SOPC技術加載Altera公司的IP core形成一個以NiosII CPU為核心的,TCP/IP和JTAG IP core端口為通信模塊的硬件平臺。軟件部分包括網絡傳輸處理和JTAG IP core接口程序部分。

JTAG IP core是業務信號處理邏輯模塊,可以是ARM、PowerPC、MIPS等不同架構的嵌入式處理器。

1.1 核心子系統設計

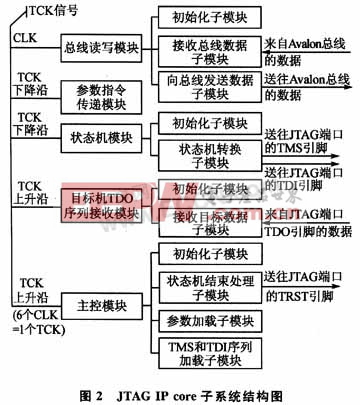

JTAG IP core是系統的核心部分。它負責目標機調試命令的格式轉換、傳送邏輯控制,以及JTAG狀態機狀態轉換的控制。JTAG IP core子系統劃分為5個模塊,每個模塊又由子模塊所構成。模塊的執行次序不同,或并發,或順序執行。JTAG IP core子系統結構圖如圖2所示。

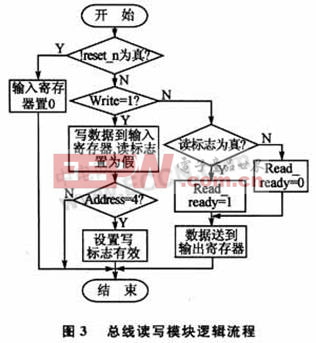

總線讀寫模塊負責接收參數和指令,同時將處理后的數據輸出到總線。接收總線數據子模塊接收Avalon總線的數據并更新標志位;讀信號觸發向總線發送數據子模塊進行數據傳輸。總線讀寫模塊邏輯流程如圖3所示。

評論