電子記帳控稅終端機設計的片上系統SOC芯片研究

1 引 言

電子記帳控稅終端機屬于高度安全和可靠的產品,關系到信息安全和金融安全,長期使用國外的核心器件將給國家安全帶來嚴重隱患。擁有自主知識產權的嵌入式處理器、專用芯片及其嵌入式操作系統已成為振興我國電子行業的當務之急。

目前國家正在大力發展金稅工程,本文作者參與了針對電子記帳控稅終端機設計的片上系統(System on Chip,SOC)芯片的研究。

2 總體方案

本SoC芯片是面向電子記帳終端設備而設計的符合國家電子記帳終端設備標準的高性能嵌入式的系統芯片,其中以32位的SPARC V8架構的處理器為內核,集成了符合ISO7816標準的智能卡控制器和符合ISO7811/2標準的磁卡控制器接口等外圍設備。他的應用既降低了電子記帳終端設備的成本,又大大提高了系統的可靠性。

2.1 SoC的結構

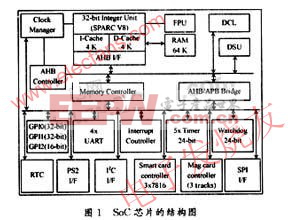

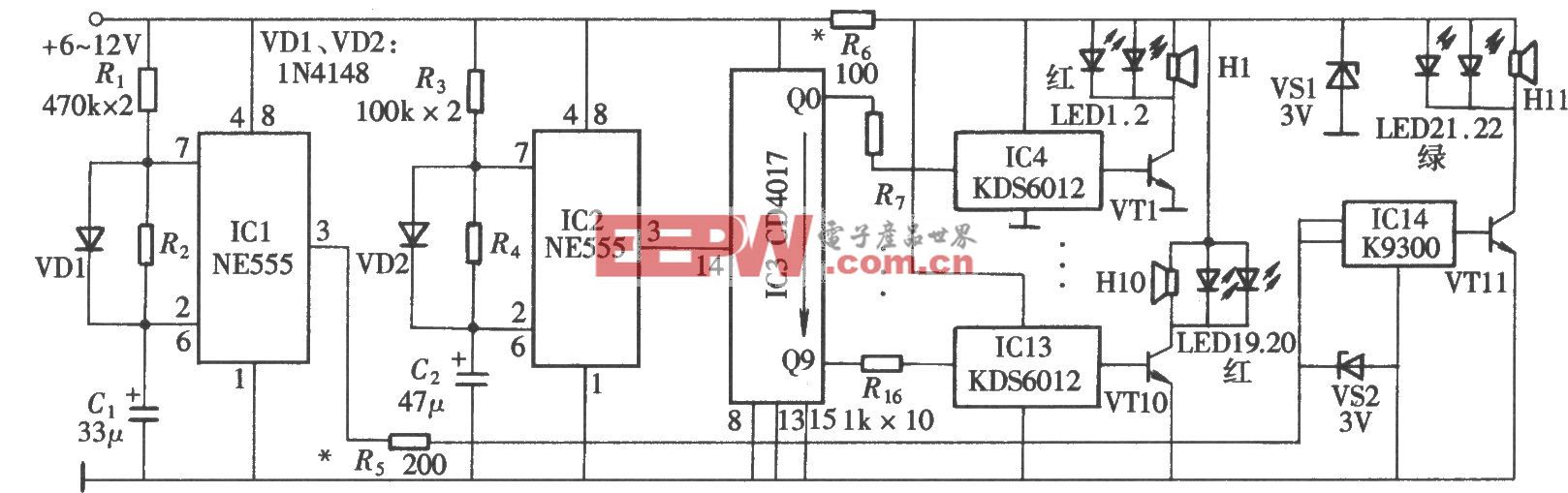

本SoC芯片內部采用可裁減的總線式結構,選用ARM公司的AMBA總線作為SoC內部總線,總線上各個模塊采用統一的接口方式和總線連接,從而實現了模塊開發的標準化,降低了開發的工作量。本SoC芯片的結構如圖1所示。

本SoC采用Harvard結構,地址總線和數據總線分開,分別連接到獨立的cache控制器上。指令cache和數據cache均為直接映射cache,配置各為4 kB;各部分的功能簡述如下:

(1)32位整型數處理單元(Integer Unit,IU)支持SPARC V8指令集。IU的主要功能是執行整數運算、計算要訪問的存儲器的地址,另外他也支持指令計數器和控制指令的執行。IU具有以下特點:

①5級單一指令流水;

②單獨的指令cache和數據cache;

③標準的8個寄存器窗口;

④硬件乘法、除法器;

⑤帶40位累加器的16×16位MAC。

(2)浮點運算單元(Floating Point Unit,FPU)提供遵循SPARC V8標準的全部浮點指令,其浮點數據的格式和浮點指令遵循ANSI/IEEE 754-1985標準,FPU連接在IU上。FPU有32個32 b的浮點寄存器。芯片使用標準的LD/ST指令在FPU和存儲器之間移動數據。存儲器地址由IU計算,浮點操作指令完成浮點算術運算。

內部的AMBA總線包括2種總線:AHB和APB。APB總線用來訪問片內外設的寄存器;AHB總線用作高速數據傳輸。AHB總線連接處理器cache控制器和其他的高速單元,IU是總線上惟一的主控單元。AHB總線從屬單元有:存儲器控制器、AHB/APB轉換橋等。AHB/APB轉換橋作為一個從屬設備連接在AHB總線上,是APB總線惟一的主控單元,處理器通過AHB/APB橋訪問大部分片內外設。

(3)SOC的片上外設,智能卡控制器(Smartcard controller):符合ISO7816標準:

磁條卡控制(magnetic stripe card Controller):符合ISO7811/2標準;

通用輸入輸出接口(GPIO):共80個GPIO端口;

評論