基于DSP的1553B總線系統設計與實現

摘要:在研究1553B總線協議特點的基礎上,提出了一種基于DSP的1553B總線接口設計方案.詳細描述了硬件電路的實現及軟件驅動程序的編寫。在電路中采用DSPTMS320F2812為核心處理單元。BU-64843為1553B協議執行元件,采用FPGA實現地址譯碼和邏輯控制功能。為了保證1553B總線消息處理的實時性,直接由下位機DSP控制1553B協議芯片,負責消息的讀取、處理、寫入和1553B協議芯片的初始化,通過對BU-64843寄存器的配置,使系統工作在BC/RT/MT模式。通信協議處理模塊嚴格按照通信協議收發周期性消息,時間誤差精度小于1μs。

關鍵詞:1553B;總線接口;DSP;FPGA;TMS320F2812

航空電子綜合化是一種在苛刻的空間限制條件下,對密集型的航空電子子系統集合進行信息綜合和功能綜合的技術。以MIL-STD-1553B為代表的子系統聯網接口標準構成了目前航空電子綜合系統中信息交換的主干道。1553B總線接口電路是實現航空電子綜合化系統的關鍵部件,其作用是在1553B總線與現有的其他總線技術之間搭建一座橋梁,使得不同制式的信息流能夠實時、準確地進行相互轉換。在1553B總線接口的研制過程中,復雜而苛刻的環境對中央處理器的實時性與可靠性提出了很高的要求,而DSP芯片以其優良的高速性能為中央處理器的選擇提供了一個較為理想的解決方案。

隨著MIL-STD-1553B總線協議標準的頒布。許多公司開發了總線與CPU之間的硬件接口芯片。在實際的1553B總線工程中使用最為廣泛的是DDC公司生產的接口芯片。這些芯片完全實現了1553B總線的電氣特性協議,而且與CPU或存儲器連接非常簡單。本文探討基于TMS320F2812(以下簡稱F2812)和DDC公司的BU-64843協議芯片的1553B總線接口的硬件設計和軟件驅動編寫要點。

1 1553B總線

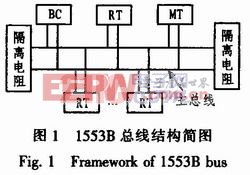

1553B總線是一種時分制指令/響應式多路傳輸數據總線,具有很高的可靠性和良好的實時性。1553B總線由4種基本硬件組成:傳輸介質、總線控制器(BC)、遠程終端(RT)、總線監視器(MT)。

1553B總線采用異步、半雙工方式傳輸,傳輸速率1 MB/s。1553B總線傳輸協議規定的傳輸過程為:BC向某一終端發送一個接收/發送指令,RT在規定的響應時間內發回一個狀態字并執行消息的接收/發送。在操作過程中BC始終掌握總線的控制權,總線上任何時候只有一個BC,但可以最多掛31個RT或MT。在總線的數據傳輸過程中,MT按要求監視總線上的數據,并將這些數據輸出或者存盤以便實時地監測這些數據的傳輸狀態或便于后續分析。1553B采用雙冗余總線,有2個傳輸通道,保證了良好的容錯性和故障隔離。如果當前總線的數據傳輸出現錯誤或故障,數據可以自動從冗余總線上傳輸。1553B總線的傳輸介質為屏蔽雙絞線。其總線結構簡圖如圖l所示。

2 系統設計方案

該系統以F2812為控制核心,與外圍輔助電路構成微計算機系統;由BU-64843協議芯片完成1553B總線的功能。BU-64843提供了豐富的資源。為軟件的設計提供了極大的靈活性和可靠性;控制和譯碼信號利用FPGA實現,FPGA器件電路連接簡單,使用方便,使用功能強大的VerilogHDL語言編程,可提高系統的維護性和擴展性。

F2812負責消息的讀取、處理、寫入和BU-64843協議芯片的初始化。通過對BU-64843的相關寄存器進行相應的配置,就可以使本接口卡工作在BC模式、RT模式或MT模式。接口卡在BC模式下實現1553B總線消息的接收,BU-64843協議芯片每接收完一個消息,就向F2812發送一次中斷申請,由F2812響應中斷并從相應的RAM區讀取接收到的消息進行相應處理,F2812同時完成與上位機的通訊,并把接收到的數據發送出去。與上位機的通訊是利用F2812的串行通信接口(SCI),本系統采用MAX485實現的。

評論