基于DSP+ARM架構的協議轉換器設計

摘要:介紹基于DSP+ARM架構協議轉換器的系統組成及其工作原理,給出了DSP通過EMIF接口與FPGA無縫連接的接口實現,DSP通過HPI接口與ARM高速接口的實現,以及基于ARM的高速以太網接口。簡要介紹了基于嵌入式操作系統;uClinux的網絡編程,給出了實驗結果。

本文引用地址:http://www.j9360.com/article/151317.htm在測試飛行控制組件時,遙測接收設各離信息處理中心較遠,而被測數據量又極大,如果采用傳統的專線傳輸遙測數據,則傳輸時間需幾個小時,無法滿足快速處理的要求。因此,需要研制一種協議轉換器,用來完成被測數據無損、實時、遠距離地與遠程上位機進行通信,并能接收上位機的控制指令,實現工作狀態的遠程交互,而測試人員通過上位機的人機界面就可以完成所有測試。

1、系統組成及工作原理

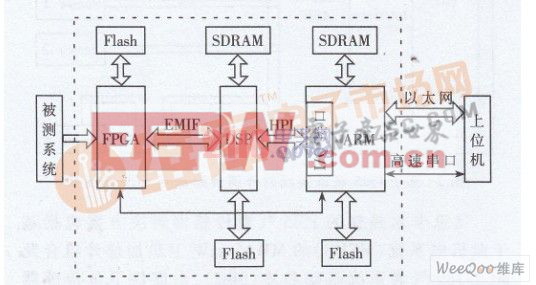

考慮到系統實時性和可靠性的要求,選擇以太網口作為協議轉換器與遠程上位機的數據轉發接口、以高速串口作為控制口的通信方式,采用DSP+ARM架構的硬件解決方案。系統框圖如圖1所示。基本工作原理:FPGA作為數據預處理器,完成并行數據到串行數據的轉換等數據預處理任務;DSP讀取FPGA處理后的數據并完成數據壓縮;ARM作為中央處理控制器,主要從DSP系統中讀取已經編碼的數據并通過以太網完成與上位機實時通信的任務。上位機按照數據傳輸協議、產品的數據遙測協議解調出各類物理變量,記錄并存儲。

圖1協議轉換器系統框圖

測試人員通過上位機完成工作狀態的遠程設置與查詢信息交互的任務。

2、硬件設計

2.1 TMS32OC6416及其外圍電路設計

DSP芯片選用TI公司的TMS320C6416。這是TI公司推出的高速定點DSP,它擁有處理能力強大的CPU、高達1 MB的RAM及豐富的外設接口。外設包括為CPU訪問外圍設備提供無縫接口的靈活的外部存儲器接口EMIFA和EMIFB,一個使得DSP很容易通過PCI接口無縫連接到具有PCI功能的外部主CPU上的PCI接口,一個16/32 bit寬的異步并行接口HPI(和Pal共用相同的引腳),一個提供64 bit數據通道訪問的增強型EDMA等。TMS320C6416采用3.3 V和1.4 V電源供電,其中I/O采用3.3 V電源供電,內核采用1,4 V電源供電。TMS320C6416有符合IEEE1149,1標準的JTAG標準測試接口及相應的控制器,從而可以通過仿真器把DSP系統與PC機相連,進行在線調試。

2.1.1 DSP與SDRAM、Flash的接口電路

DSP處理器TMS320C6416對外有2個EMIF總線接口,分別是寬64 bit的EMIFA和寬16 bit的EMIFB。EMIFA接口具各與8、16、32、64 bit系統接口的功能,EMIFB接口端口支持8 bit和16 bit系統。EMIFA分成ACE0~ACE3四個存儲空間,每個存儲空間可以獨立配置,無縫連接多種類型的存儲器(如SRAM、Flash RAM、DDR RAM)。

為了提高系統運行速度,外擴兩片SDRAM芯片作為程序的運行空間、數據及堆棧區。SDRAM芯片選用同步存儲器MT48LC2M32B2TG,其容量為2 M×32 bit。TMS-320C6416通過EMIFA接口實現與兩片SDRAM芯片的無縫連接。

TMS320C64l6內部沒有Flash存儲器,為了形成獨立的系統,采用外部擴展Flash存儲器AM29LV400B存儲程序。系統復位時,從Flash中加載程序。TMS320C6416通過EMIFB接口實現與Flash芯片的無縫連接。

2.1.2 DSP與FPGA的接口電路

由于DSP處理器TMS320C6416的采樣速度及存儲空間受到自身約束限制,所以數據的采集、流向控制和數據預處理等任務由FPGA完成。FPGA芯片選用Xilinx公司低成本現場可編程門陣列Spartan -3E系列中的XC3S500E。XC3S500E芯片集成有⒛個Block RAM,每個RAM塊中的18 Kbit的模塊存儲器是完全同步、真正的雙端存儲器。用戶可獨立地從每個端口讀出或向每個端口寫人(但同一地址不能同時進行讀和寫)。另外,每個端口都有一個獨立的時鐘,并且對每個端口的數據寬度都可以獨立進行配置。

評論