利用可配置處理器來創建多標準多分辨率視頻引擎

隨著消費類電子產品,尤其是手機、PDA和便攜式媒體播放器(PMP)的急劇發展,其對于終端硅供應商的要求也大大提高。對這些供應商來說,設計僅僅能夠適用于一到兩個多媒體編解碼器或無線標準的IC已經遠遠不夠了。消費者希望他們的設備能夠播放各種采用不同的編碼標準和無線下載標準的媒體。因此,必須采取一個新的更具靈活性的途徑來更好地適配新的媒體標準。在本文中,我們主要談一談視頻解碼器和編碼器引擎所面對的挑戰和機遇。

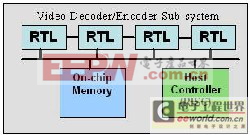

本文引用地址:http://www.j9360.com/article/151141.htm上一代視頻ASIC設計的目的是為了解碼和編碼MPEG-2,因為這是DVD所使用的標準。其中也有些支持MPEG-1,可以播放VCD。大多數情況下,這種單個應用的邏輯實現策略就是:利用RTL(寄存器轉換層,寄存器轉換邏輯)來設計定制化MPEG-2解碼器和編碼器。下圖1是一個典型的MPEG-2視頻ASIC結構,展示了由視頻子系統、主控制器和片上存儲器組成的RTL功能塊。

圖1:典型的MPEG-2視頻ASIC結構

隨著市場形勢的改變,現在的視頻ASIC必須能夠支持多種視頻標準,并具有多個分辨率。由于下列原因,傳統的RTL方法已經不再有效:

·隨著標準數量的增加,RTL功能塊的數量和復雜性也增加;

·無論是執行一個新的視頻標準,還是升級現有的已執行的標準,或者修改bug,都需要進行硅芯片重制;

·在第一代硅執行之后的這4-5年內,視頻編解碼器,尤其是編碼器在性能上(比特率、性能)有很大的改進。要執行這些改進的成果,也必須在所有的RTL方法中進行硅芯片重制。

那么,有沒有其它辦法呢?使用一個可編程處理器是最佳方案,因為它可以解決上面提到的所有問題:(1)處理器和編解碼器之間很容易建立連接端口;(不論是采用新的視頻標準,還是升級現有的編解碼器或者修改bug,都可以很容易地在軟件中進行);(3)通過軟件升級,可以很容易地應用視頻編解碼器執行中的改進。

但是,由于其性能瓶頸,傳統的處理器只能用于一般的編碼,而不能用于視頻引擎。嵌入式DSP也不是專為視頻而設計的,但擁有通用DSP應用所需的硬件功能單元、指令和接口。因此,要在傳統的RISC和DSP處理器上執行視頻編解碼,就意味著這些處理器必須以非常高的速度運行(MHz),而且還需要大量內存并消耗大量功率,但是在便攜式設備中,這顯然是行不通的。

只要我們對某個視頻內核中所需的計算次數作一個簡單分析,就很容易得出這一點。絕對誤差和是大多數視頻解碼運算的動作估計中所進行的一個重要計算步驟。SAD運算的目的在于發現兩個連續視頻幀之間的宏模塊的運動。它是通過計算這兩個宏模塊中每套相應的象素值之間的絕對誤差之和來實現這一目的的。

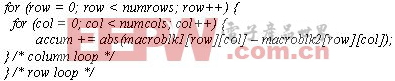

下面的C代碼展示了SAD運算的一次簡單執行:

圖2展示了SAD運算中的基本計算步驟。如圖所示,其中主要進行的計算有減、算絕對值和結果累計。

圖2:絕對誤差和(SAD)內核中進行的主要計算

計算一個RISC上的兩個16x16宏模塊的SAD需要進行256次減法、256次求絕對值和256次相加DD總共進行了768次計算,還不包括傳輸數據所需的負載與內存。由于每一幀當中所有的宏模塊都必須進行這一運算,很顯然這在計算上成本是很昂貴的,而且會隨著視頻幀分辨率的增加而越來越難。

實際上,在一個帶有一些如相乘和乘法累加等指令的中等范圍通用型RISC處理器上,如果要以CIF的分辨率進行H。26?Baseline解碼,需要250MHz的速率,而如果進行H。26?Baseline編碼,所需速率更是超過1GHz。這意味著光是處理器內核就要消耗將近500mW的功率,更不用提內存和視頻片上系統中其它部分消耗的功率了。很顯然這種處理器不能作為嵌入式多媒體處理器用于便攜式設備中。

評論