基于DSP的磁存儲設備抗沖擊技術控制系統

1 前言

本文引用地址:http://www.j9360.com/article/150410.htm本文采用了外加固主動控制理論與技術,將電磁主動控制技術用于計算機外部設備(微型盤)的振動沖擊外加固,并且構建了以DSP 為硬件平臺的數字主動控制系統[1]。

2 數字控制系統的硬件設計

從1982年TI(美國德州儀器公司)推出通用可編 程DSP芯片以來,DSP技術取得了迅猛的發展。目前DSP芯片市場中,主要由TI,ADI,ATT和Motorola公司占據。本文綜合實際要求,采用一款由TI公司生產的新型16位定點DSP芯片:TMS320F243[2],他集成了A/D,PWM調制等幾種先進外設,特別適于對電機的數字化控制。

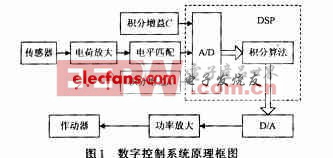

2.1 控制系統原理

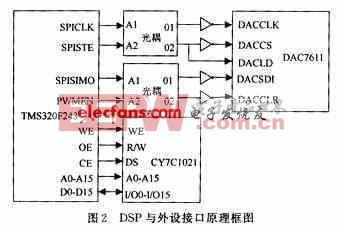

數字信號處理器(DSP)具有實時信號處理能力和強大的運算功能。該系統的工作原理是基礎加速度傳感器拾取基礎振動沖擊加速度信號,然后送入前置放大器,由DSP將電荷放大器輸出信號經A/D采樣后,完成對信號的一次積分(轉換為速度信號)和二次積分(轉換為位移信號)運算,將兩次積分結果做求和運算,再將結果經D/A轉換后輸入到功率放大器,最后將功率放大器輸出信號以控制電壓的形式加在執行機構上,執行機構會產生相應的作動力來抵消來自基礎的振動和沖擊。由于DSP片內集成了10 b的A/D,所以可直接將模擬信號與DSP相接,圖1是整個數字控制系統的原理框圖。的DAC7611。由于DSP內部10 b A/D的電壓輸入范圍為0~5 V,輸入信號經A/D轉換后由數值0~1 023(十進制數)來分別對應0~5 V的電壓信號。所以DSP的輸入信號已不是正負對稱信號,并且系統中DAC7611的輸出范圍為0~4.095 V,而系統后級中功放的輸入應是零均值的,所以需要對DAC輸出信號利用運算放大器進行電平變換。

另外,DAC7611對于時鐘信號的要求非常嚴格。 他要求其時鐘信號的上升沿發生在每一位數據的傳送過程中。TMS320F243的SPI(串行外設接口)是一個高速、同步串行I/O口,他可以設置每次產生的串行數據流的位數(1~16位),并且對于位傳輸速度也可以編程控制。

SPI的時鐘輸出信號線SPICLK能夠提供4種類型的時鐘信號。其中有一種帶延時的上升沿時鐘,可使SPI在上升沿之前的半個周期內發送數據,或在SPICLK信號上升沿后接收數據。這恰好符合DAC7611時鐘信號的要求。

由于DSP片內資源有限,設計中在片外擴展了用于存放數據的RAMCY71021,其讀寫時間為12 ns,與DSP的速度匹配。并且該芯片在未被操作時會自動采用低功耗工作方式。在利用DSP的串行外設接口向D/A傳送數據時,系統還采用光耦器件將數、模電路進行隔離。外圍接口電路如圖2所示。

由于系統加電后,程序首先是從片內的FLSH程序ROM開始執行的,所以一定要把引腳MP/MC接成微處理器方式。

評論