基于DM642的X.264編碼器優化

摘要:X.264編碼器注重實效性,在不明顯降低編碼性能的前提下,降低編碼的計算復雜度,摒棄了JM中一些耗時相對較大但對性能的提升影響很小的模塊,因此嵌入式系統中常選用X.264編碼器。移植到DSP平臺的X.264編碼器,編碼效率不佳,平均只有0.7 f/s。為了能夠在DSP平臺上進行高效率的鳊碼,采用了代碼優化以及DM642優化2種優化方式來優化移植到DM642平臺的X.264編碼器。對優化過后的X.264編碼器在DM642平臺上進行了實驗。實驗結果表明,優化過后的X.264編碼器對CIF格式視頻序列的編碼時間大幅度的降低。

關鍵詞:X.264;DM642;軟件流水;函數合并;EDMA

0 引言

H.264標準的全稱為“H.264/MPEG-4 part 10”,是由ITU-T和ISO/IEC共同成立的聯合視頻組(Joint Video Team,JVT)制定的新標準。H.264依然采用預測結合變換的混合編碼方案,為了在相同的編碼框架下得到更高的視頻壓縮編碼性能和更廣泛的適用性,H.264標準引入了許多新技術,如1/4,1/8像素精度的運動估計、多參考幀的幀間預測、幀內預測、環路濾波和自適應算術編碼等。H.264視頻編碼標準在編碼質量和壓縮比上比原有的視頻編碼標準都有了明顯的提高。

在相同的視覺感知質量上,編碼效率比之前的編碼方式提高了50%。H.264標準的編碼性能超越了以往所有的視頻編碼標準,具有很好的應用前景,大量的應用于視頻壓縮和視頻監控。

目前,H.264編解碼標準的研究主要分為算法研究和硬件實現兩大類,硬件實現的方案主要分為3種:

(1)基于PC平臺的方案。此方案為純軟件實現編解碼,利用MMX和SSE/SSE2等多媒體指令集來優化程序,具有開發成本低和周期短等優點。PC機的CPU體系結構并不適合處理數字信號,故CPU的有效利用率比較低。

(2)基于ASIC芯片的純硬件方案。此方案將視頻編解碼算法固化成硬件,具有集成度高和開發周期短等優點,但是專用型比較強,產品不易升級。目前市場上已經出現了H.264的編解碼芯片,如Fujitsu的MB86H51、Hisilcon的GOALTMHi3510和JVC公司的JCY0237 LSI等。

(3)基于DSP的軟硬件結合方案。此方案利用DSP芯片和其它外圍芯片來構成處理系統,具有開發靈活性高、處理能力強、開發周期低、功耗低和易升級等優點。隨著DSP性價比的不斷提高,該方案已經成為目前H.264編碼器硬件實現的理想方案。

H.264編解碼標準具有壓縮比高、適應性廣、容錯能力強和圖像恢復質量高等特點,在實時系統中具有很好的應用前景。TMS320DM642是TI公司推出的一款針對視頻和圖像處理領域應用的數字多媒體處理芯片,具有處理能力強和集成度高等特點,是目前實現H.264視頻編碼器的理想芯片之一。很多國內外公司都在開發或已經開發出了基于DM642開發視頻監控系統。

1 X.264編碼器移植

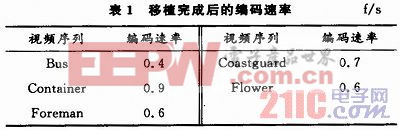

X.264是由法國巴黎中心學校的中心研究所于2004年6月發起,由許多視頻愛好者共同完成的項目,它注重實效性,在不明顯降低編碼性能的前提下,努力降低編碼的計算復雜度,摒棄了JM中一些耗時相對較大但對性能的提升影響很小的模塊,如多參考幀、幀間預測中不必要的塊模式、CABAC等。X.264編碼器在程序結構上,利用了MMX/SSE/SSE2等基于X86構架的多媒體硬件加速指令。需要將相關的X86指令屏蔽,對部分函數進行精簡,使其結構簡單易于在DSP上執行。簡單移植過后的X.264編碼器,在DM642平臺上的編碼效率極低,表1為移植過后的X.264編碼器在DM642平臺上編碼結果。

由結果可以看出,移植完成后的X.264在DM642平臺上的編碼效率非常低,只能達到平均0.6 f/s的編碼速率,需要進一步針對X.264編碼器和DM642的特性來優化以提高編碼效率。

評論