DSP實現EAS掃頻信號源設計

1 引言

商品防竊監視器(Electronic Article Surveillance)簡稱EAS,是目前超市普遍使用的安檢防竊設備。其原理是由發射電路產生7.8MHz~8.8MHz的掃頻信號,該信號由近場天線發射,當天線附近有標簽存在時(標簽為高Q值的LC振蕩回路,諧振中心頻率為7.8MHz),標簽發出諧振電磁波信號,該信號被EAS接收天線接收,經解調、放大和數字化處理后,最終發出報警信息。傳統的掃頻信號發生電路由于分立元件參數的一致性差,振蕩頻率難以精確控制,頻率變化的線性度、掃頻寬度等諸多指標也受到元件性能的嚴格約束。筆者采用AD公司的AD9834型DDS實現掃頻信號合成,同時,考慮到信號的高速頻率變化特點,需使用數字信號處理器(DSP)對AD9834進行控制。筆者采用TI公司的TMS320VC5410型數字信號處理器(以下簡稱C5410)。下面介紹這些器件的特點及電路實現方法。

2 TMS320VC5410和AD9834簡介

本設計要求C5410通過多通道緩沖串行口向AD9834發送命令和數據,由AD9834產生EAS系統需要的掃頻信號。C5410是TI公司生產的新一代低功耗TMS320C5000系列定點數字信號處理器,它有3個高速、全雙工、多通道緩沖串行口(McBSP),每個串行口可以支持128個通道,速度可達100Mb/s。該系列提供的McBSP支持多種串行通信的方式和協議,可以根據用戶的不同需要進行配置。多通道緩沖串行口遵循SPI協議是以主從方式工作的,這種模式通常有1個主設備和1個或多個從設備,其接口包括以下4種信號:串行數據輸入(也稱為主進從出或MISO);串行數據輸出(也稱為主出從進或MOSI);串行移位時鐘(也稱為SCK);從使能信號(也稱為SS)。McBSP的時鐘停止模式與SPI協議兼容,當McBSP處于時鐘停止模式時,發送器和接收器是內部同步的。

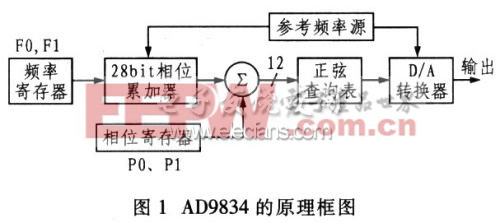

AD9834的原理框圖如圖1所示。它使用的DDS技術是一種利用正弦信號相位線性增加的原理直接由數字累加和數/模轉換合成所需頻率的技術。AD9834主要由數控振蕩器(NCO)、相位調制器、正弦查詢表ROM和1個10位D/A轉換器組成。數控振蕩器和相位調制器主要由2個頻率選擇寄存器、1個相位累加器、2個相位偏移寄存器和1個相位偏移加法器構成,它的最高工作頻率可達50MHz。

AD9834的頻率控制字由式(1)求得

式中,0Δphase228-1,fMCLK最高可達50MHz,它是由高穩定度晶體振蕩器獲得或由其他器件編程提供,用來同步整個合成器的各個組成部分。

相位控制字由式(2)求得

ΔP=Kx2π/4096 (2)

式中,0小于K小于228-1,改變K值即可改變輸出相位值。

3 系統設計思想

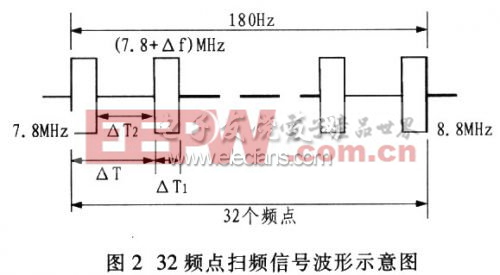

傳統的EAS掃頻信號產生電路使用了壓控振蕩集成電路。通過改變外圍變容二極管的直流偏壓可以使掃頻信號的頻率范圍控制在8.2MHz±0.5MHz。當采用全數字頻率合成時,由于數字信號的非連續性,不可能產生連續的掃頻信號,只能產生臺階性變化的掃頻信號,即1個單頻點持續一段時間后增加4,,再跳躍到另1個單頻點,因此,如果掃頻信號的掃頻范圍為8.2MHz±-O.5MHz,將該lMHz頻率跨度等分為32個頻點,于是相鄰頻點之間的頻率間隔Δf=1MHz/31=0.0323MHz。如果掃頻信號的掃頻周期為 180Hz(即5.6ms),則每個頻點占用的時間為ΔT=5.6ms/3l=181pμs。該ΔT又分為二部分,第一部分△T1為振蕩時間,即單頻率波形持續時間;第二部分ΔT2為延時等待時間,在這段時間內理論上沒有波形輸出。在實際應用中可通過動態改變△T2在ΔT中所占的比例以控制EAS的發射功率,對系統很有用。如果每個單頻率波形持續時間(頻率振蕩時間)△T1=10μs,則每個單頻率波形的延時等待時間ΔT2=(5.6-0.01x32)/31=170.3μs。多通道緩沖串行口發送1個單頻率字只需71μs左右,能夠完成控制字和頻率字的發送,而且還能夠在此時間內完成復雜的計算。圖2為180Hz周期內完成的32頻點掃頻信號波形示意圖。其中,每個頻點展開后都是頻率一定的正弦波,每個周期內32頻點掃頻信號的頻率范圍都是從7.7MHz到8.7MHz臺階性變化。

4.1 硬件設計方案

基于上述設計思想的硬件連接方案如圖3所示,包括C5410、10MHz晶體振蕩器、AD9834及濾波放大電路。由于AD9834的電源電壓在2.3V到5.5V范圍內可選,C5410的電源電壓為3.3V。所以在連接時無需電平轉換。10MHz晶體振蕩器向C5410提供輸入時鐘。初始化C5410使其工作頻率為100MHz,因為只有此時才能使其定時器周期寄存器從TOUT引腳輸出50MHz時鐘信號。該時鐘信號輸出到AD9834的MCLK腳,作為AD9834的工作時鐘。理論分析指出:輸出信號的相位噪聲取決于時鐘信號的相位噪聲,在輸出信號頻率不變的情況下,輸入時鐘信號頻率越高,相位噪聲惡化越小。

濾波放大電路對AD9834輸出的掃頻波信號進行進一步濾波處理和幅度放大,以濾除高頻信號干擾和噪聲,將信噪比控制在允許范圍內。由于雜波信號干擾,從AD9834出來的掃頻信號在沒有濾波的情況下含有豐富的高頻成分,采用RC或LC無源濾波電路處理后可以得到一組以8.2MHz為中心頻率,掃頻范圍在7.7MHz~8.7MHz的較為清晰的掃頻波。具體實現方案是先通過由1只去耦電容器和1只電阻器組成的RC回路濾掉由:DDS輸出的掃頻信號中的高頻成分,然后使用帶有電感器的復式濾波電路(可以選擇LC濾波電路),經電感器濾波后不但負載電流及電壓的脈動減小,而且波形也變得平滑,L、c的具體值可由f=1/(LC)1/2求得,其中f=8.7MHz,濾波電路如圖4所示。由于AD9834的輸出信號幅度最大只有O.8V,所以需將其幅值放大才能作為掃頻信號源,在系統中可由1個高速運算放大器實現。

由于該電路是高速數,模混合電路,因此電磁兼容性能非常重要。特別是DSP和DDS共用1個電源,使得器件的工作信號通過電源線傳輸形成干擾。通常必須在電源接入處并人大容量的電解電容器和鉭電容器,濾除低頻噪聲。還應該在每個器件的電源引腳處接1只0.01pF一0.1pF的去耦電容器。

評論