基于DSP和FPGA的多波形雷達回波中頻模擬器實現

本文論述一種自主產生式的雷達回波模擬器中頻部分的設計實現方法,該模擬器可產生脈沖單頻、脈沖線性調頻、步進頻、步進頻+線性調頻等多種波形的雷達回波信號,并可產生雙目標和參數可控的帶限高斯白噪聲,可模擬主要的干擾類型;輸出信號既可以直接用于信號處理機的中頻注入式測試,也可上變頻后用于雷達系統的射頻條件下的各種測試驗證。以下對該中頻雷達回波模擬器的實現方法予以詳細闡述。

本文引用地址:http://www.j9360.com/article/150267.htm1 回波信號理論分析

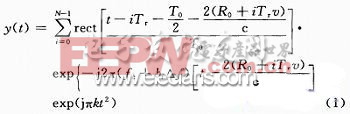

按照設計要求,該模擬器需要模擬脈沖單頻、脈沖線性調頻、步進頻、步進頻+線性調頻共四種波形的信號。其中,步進頻又包括順序步進頻和隨機步進頻兩種類型。這些波形的雷達回波信號,均可以統一表示為式(1)的形式:

式中:c為光速;N為相參幀的脈沖總個數;i表示相參幀內的第幾個脈沖;To為脈沖寬度;Tr為脈沖周期;fc為相參幀內首脈沖的載頻;△f為脈沖間最小步進頻差;bi△f為第i個脈沖在初始載頻基礎上的頻率變化(僅適用于脈間頻率捷變波形,非脈間捷變波形則bi=0);k為線性調頻波形時的脈內調頻變化率(非脈內線性調頻則k=0);Ro為目標當前距離;v為目標當前速度。

由以上分析可知,無論上述何種波形,均可根據式(1)計算脈沖的延時、每個脈沖的脈內初相、以及每個脈沖的載頻等參數,并對這些參數在與產品同步的基礎上予以實時控制來進行模擬實現。根據發射波形,還要決定是否添加脈內頻率線性調制。

2 回波模擬器系統設計

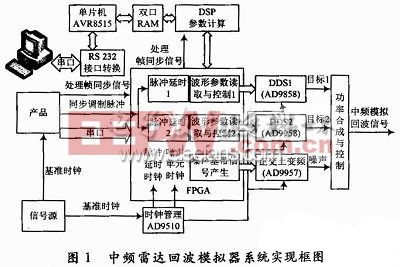

根據系統需求和前述雷達回波信號理論分析,該中頻雷達回波模擬器(以下簡稱模擬器)采用了如圖1所示的系統實現方案。

該模擬器通過單片機(AVR8515)與上位機進行異步串行通信,單片機完成通信協議的解包、打包等過程,接收上位機中用戶設定的目標和干擾參數,發送模擬器的實時模擬狀態信息給上位機。系統以DSP(ADSP-21060)作為脈沖參數的實時計算單元,單片機與DSP問通過雙口RAM進行信息交換。DSP得到兩個目標的模擬參數后,根據參數變化的時間節拍,計算一個相參幀兩目標的各脈沖的初相、載頻、脈沖延時等參數,并寫給雙口RAM。系統以FPGA(XC2V3000)作為信號處理與控制單元,FPGA讀取后,在產品提供的處理幀同步信號和同步調制脈沖控制下,結合產品串口傳過來的波形類型的信息(如:脈內單頻還是線性調頻),形成兩個目標的延時脈沖,并控制兩個目標各自的DDS(AD9858)信號產生單元,產生出兩個目標信號。帶限的高斯白噪聲的數字正交基帶也由FPGA產生,并同步AD9957的數字正交上變頻功能將基帶調制到所需的中心頻上。目標1、目標2和噪聲信號的合成由模擬電路實現,并實現一定的功率控制,最后輸出所需的中頻雷達回波信號。模擬器系統各單元時鐘的相參性至關重要,由專用時鐘管理芯片(AD9510)產生FPGA,AD9858,AD9957的工作時鐘。

評論