基于DSP的SOPC技術設計

結合Altera公司推出的Nios II嵌入式軟核處理器,提出一種具有常規DSP處理器功能的NiosII系統SOPC解決方案;利用NiosII可自定叉指令的特點。

本文引用地址:http://www.j9360.com/article/150152.htm通過Matlab和DSP Builder或直接用VHDL設計并生成復數乘法器、整數乘法器和浮點乘法器等硬件模塊,將它們定制為相應的指令,從而將軟件的靈活性和硬件的高速性結合起來,較好地解決了傳統DSP處理器所面臨的速度問題、硬件結構不可重構性問題、開發升級周期長和不可移植性等問題。

隨著微電子技術和計算機工具軟件的發展,可編程片上系統SOPC的設計理念和設計方法成為了一種趨勢。為了解決傳統DSP處理器所面臨的速度問題、硬件結構不可重構性問題、開發升級周期長和不可移植性等問題,我們應用Altera公司推出的Nios II嵌入式軟核處理器,提出了一種具有常規

DSP處理器功能的Nios II系統SOPC解決方案。

由于可編輯的Nios II核含有許多可配置的接口模塊核,因此用戶可根據設計要求,利用Quar-tusII和SOPC Builder對NiosII及其外圍系統進行構建。而且用戶可通過Matlab和DSP Builder,或直接用VHDL等硬件描述語言設計,為Nios II嵌入式處理器設計各類硬件模塊,并以指令的形式加入Nios II的指令系統,從而成為Nios II系統的一個接口設備,與整個片內嵌入式系統融為一體,而不是直接下載到FPGA中生成龐大的硬件系統。正是Nios II所具有的這些重要特點,使得可重構單片DSP處理器功能系統的設計成為可能。

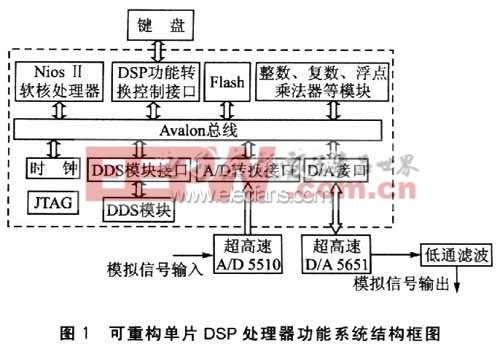

1 系統結構

本系統為單片DSP可重構系統,能實現數字信號處理方面各種功能。其中,Nios II軟核處理器的建立,主要起人機交互和控制作用。FPGA的邏輯模塊從Nios II處理器接收控制信號和數據后,實現相應的硬件功能。系統結構框圖如圖l所示。除了軟核處理器Nios II外,存儲器和I/O接口以及FIR數字濾波器、IIR數字濾波器和DDS等應用模塊均可作為外設嵌入在FPGA中。這樣,整個DSP的數字信號處理部分全部集成在FPGA器件中,各模塊均受Nios II處理器的控制。Nios II處理器系統中有Avalon總線,它規定了控制器與從屬模塊間的端口連接以及模塊閫通信的時序。數字頻率合成器DDS通過Avalon總線與Nios II處理器相連,能很方便地完成控制及數據傳送。

本系統的FPGA采用Cyclone EPICl2,它有12 060個邏輯單元(LE)和2個鎖相環(PLLs),提供6個輸出和層次時鐘結構以及復雜設計的時鐘管理電路。選用超高速10位D/A轉換器565l實現D/A轉換功能,轉換速率最高為150 MHz。整個系統在Nios II處理器的控制下,可實現FIR數字濾波、IIR數字濾波、快速傅里葉變換(FFT)算法、編/解碼、DDS功能模塊設計,以及由它構成的數控頻率調制、正交載波調制解調、數控相位調制等功能的信號發生器。

系統中各功能模塊的選擇,以及輸出信號調制方式和頻率的選擇,均可通過外接的按鍵自由選擇。下面構建一個具有常規DSP處理器功能的Nios II系統。

2 Nios II嵌入式系統設計流程

NiosII嵌入式處理器是Altera公司推出的一種專門為單芯片可編程系統(SOPC)設計而優化的CPU軟核,是一種面向用

戶、可以靈活定村的通用RISC(精簡指令集)嵌入式CPU。它采用Avalon總線結構通信接口,帶有增強的內存、調試和軟件功能,可采用匯編或C、C++等語言進行程序優化開發;具有32位指令集、32位數據通道和可配置的指令及數據緩沖。與普通嵌入式CPU系統的特性不同,其外設可以靈活選擇或增刪,可以自定制用戶邏輯為外設,可以允許用戶定制自己的指令集。由硬件模塊構成的自定制指令可通過硬件算法操作來完成復雜的軟件處理任務,也能訪問存儲器或Nios II系統外的接口邏輯。設計者可以使用Nios II加上外部的Flash、SRAM等,在FPGA上構建一個嵌入式處理器系統。

完整的基于Nios II的SOPC系統是一個軟硬件復合的系統,因此在設計時可分為硬件和軟件兩部分。Nios II的硬件設計是為了定制合適的CPU和外設,在SOPCBuider和Quartus II中完成。在這里,可以靈活定制NiosII CPU的許多特性甚至指令;可以使用Altera公司提供的大量IP核來加快開發Ntos II外設的速度,提高外設性能;也可使用第三方的IP核,或VHDL自己來定制外設。完成Nios II的硬件開發后,SOPC Buider可自動生成與自定義的Nios II CPU和外設系統、存儲器、外設地址映射等相對應的軟件開發包SDK;在生成的SDK基礎上,進入軟件開發流程。可使用匯編或C語言,甚至C++語言來進行嵌入式程序設計,使用GNU工具或其他第三方工具進行程序的編譯、鏈接及調試。

評論