DSP應用系統電磁兼容的設計

在電子系統設計時經常在電路中加入電容器來滿足系統工作時所要求的電源平穩和潔凈度。

根據電容在電路中的作用可分為:去耦電容、旁路電容和容納電容。去耦電容用來濾除高速器件在電源板上引起的騷擾電流;旁路電容可用來消除高頻輻射噪聲,從而抑制共模干擾;容納電容則配合去耦電容抑制由電流變化引起的噪聲。

主要的濾波技術包括:

·對電源線和所有進入PCB的信號進行濾波

·旁路快速開關器件

·旁路模擬電路的所有電源供電和基準電壓引腳

·在器件引線處對電源/地去耦

·用多級濾波抑制不同頻段的電源噪聲

3. 3 其它降噪措施

·根據系統功能和實現目標要求可以采用懸浮地、單點接地、多點接地和混合接地等不同的接地方式

·在適當的地方加屏蔽

·對有干擾的引線進行屏蔽或絞在一起以消除相互耦合

·在感性負載上用箝位二極管等

DSP系統具有高精度、小功率、快速邏輯等特點,容易受到寄生阻抗、介質吸收或高頻噪聲的影響 。在高速數字電路中,特別是在快速DSP中,時鐘電路通常是寬帶噪聲的主要和最大產生源,可產生高達300MHz或更高的的諧波干擾,應采取措施加以克服。此外,系統復位線、中斷線和控制線是較容易受到干擾的敏感設備。

一個電子系統的電磁兼容性很大程度上取決于元件的布局和導線的連接形式。當一段導線和相應的回路中有電流流動時,便產生了天線效應,向外輻射電磁能量,此能量的大小與流過電流的幅值、頻率及該電流環路所包圍的面積有關。從而形成了一個典型的電磁干擾源。

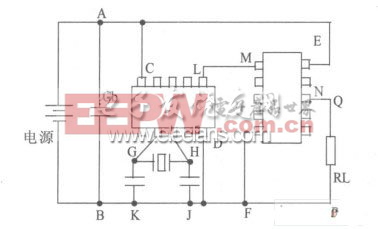

圖3 電子系統內部的電流環

如圖3所示,環路A—C—D—B和A—E—F—B中傳輸著系統正常工作所需的能量。然而電路中所消耗的能量不是恒定不變的,這主要取決于系統中各元件的瞬時工作狀態。系統中每個器件動作所引起的變化都將反映到這些傳輸線上。為了防止電流的快速變化引起的干擾,可借助電容Cb加以抑制。由信號線和控制線形成的回路N—F—P—Q 和L—M—F—D所包圍的面積相對較小,但是由它們引起的高頻噪聲也是不容忽視的。由晶振等元件組成的環路G—H—J—K,通常是系統中信號頻率最高的區域,在進行電磁兼容(EMC)設計時應當重點考慮。

由以上分析可見,在DSP應用系統設計時要重點考慮電源線、高頻信號線和時鐘振蕩電路的設計。

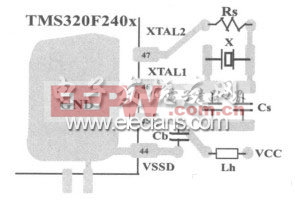

對于電源線來說,可以采用去耦電容和鐵氧體保持供電電源的穩定。信號線及其回路組成環路包圍的面積越小越好,以減小輻射干擾( EM I) 。在數字系統中時鐘信號通常是頻率最高的信號。以圖4 為例,當晶振連接C24x系列內部振蕩器時,通過減小高頻電流和電流環路包圍的面積來抑制電磁干擾。

晶振具有很高的阻抗(通常為幾百千歐) ,因此其工作時產生的高頻電流幅值很小。然而CMOS電路的輸出是含有高次諧波分量的方波信號,晶振自身對這些信號不具有高阻抗特性,從而將產生較大的諧波電流,可以加一個串聯電阻加以抑制。兩個旁路電容對振蕩器產生的高頻信號來講,呈現出低阻特性,將在Cs—X—Cs之間產生較大的電流。為了減小輻射干擾,在設計時應盡量縮小這個區域的面積。

圖中串聯電阻阻值在一千歐范圍內。

圖4 一種推薦的PCB設計方法

5 結束語

針對具體的DSP應用系統,應根據所選芯片類型和功能特點進行電磁兼容設計。例如TMS320C24x DSP,它除了配置有高速數字信號處理的結構,還具有單片電機控制的外設功能,是專門為數字電機控制和其他控制應用系統而設計的。當PCB設計完成后,還可以將C24x PWM單元設置為異步、同步或空間矢量PWM模式,進一步降低電磁干擾。增強系統的電磁兼容性。

評論