基于ARM9的SD/MMC卡控制器的ASIC設計

摘 要:文章闡述了基于TD-SCDMA手機數字基帶芯片中SD/MMC卡控制器的工作原理與應用,利用Verilog硬件描述語言對其實現。運用ModelSim進行了功能仿真,利用SMIC0.13微米工藝庫和SYNOPSYS的EDA工具對其綜合。經過FPGA驗證,確保該控制器作為一個獨立的IP核可嵌入到ASIC系統中,符合最新的SD1.0標準和MMC3.31標準。

本文引用地址:http://www.j9360.com/article/149852.htm0 引言

如今多媒體數碼產品的迅猛發展,其中,各種音頻視頻等功能的不斷增強,使得系統對于存儲介質的性能,容量,安全等方面的要求與日俱增。MMC卡和SD卡均是基于flash的存儲設備,近年來,它們以高存儲容量,快速的數據傳輸速率,加上極大的移動靈活性和更高的安全性已經成為閃存市場的標準,其廣泛應用于手機,MP3,MP4,掌上電腦等各種產品中。可見,其已經成為面向便攜式數碼電子產品的SOC芯片中通用的功能接口。

文章設計的SD/MMC控制器基于一款3G手機基帶芯片,其內核采用ARM926EJ,系統總線架構為AMBA,控制器連接到APB總線上。通過分析SD卡和MMC卡的規范,利用Verilog HDL實現了符合該規范的SD/MMC卡控制器IP核,該IP在SMIC的0.13um標準單元工藝庫下對模型進行了綜合和優化。

1 SD/MMC卡控制器工作原理

SD(Secure Digital)卡和MMC(Multi Media Card)卡是市面上常見的兩種數據存儲卡。SD卡向下兼容MMC卡。

兩者基本特性相同,只是在數據接口以及傳輸模式上有一些區別:SD卡的數據線為4根,而MMC卡只有1根;SD卡支持安全性保護;而MMC卡支持比特流傳輸(不限長傳輸,即必須接受到停止命令時才停止傳輸)。

控制器就是通過SD/MMC總線對SD/MMC卡進行初始化,讀,寫等一系列操作。其總線包括時鐘線CLK,命令線CMD,數據線DAT3-DAT0(MMC卡只有DAT0)等。上電后,控制器必須按一定的總線協議傳輸命令給卡,使其初始化。總線上一共有三種數據格式:命令包,響應包,數據包。由于在傳輸中數據和命令均有可能出錯,命令帶有7位的CRC校驗碼,數據帶有16位的CRC校驗碼。

控制器對卡進行讀操作時,將接收到的串行數據(可能是比特流,也可能是多塊)轉換為并行數據,存入FIFO.寫操作也是相同的,控制器將并行數據從FIFO里面取出,串行發出。

SD/MMC 卡的工作時鐘來源于控制器,對卡的命令或數據傳輸等一系列操作均要與該時鐘同步。該時鐘可以通過控制器進行配置,以適應不同工作狀態中卡正常工作所需的不同時鐘頻率。需要注意的是,SD 卡的最大工作頻率是25Mhz,MMC 卡的最大工作頻率是20Mhz.

總之,控制器不僅要輸出合適的工作時鐘,還要完成對命令/響應以及數據讀寫的正常工作,并針對命令和數據進行CRC 校驗,中斷的及時產生和清除。

2 控制器設計與實現

2.1 模塊劃分

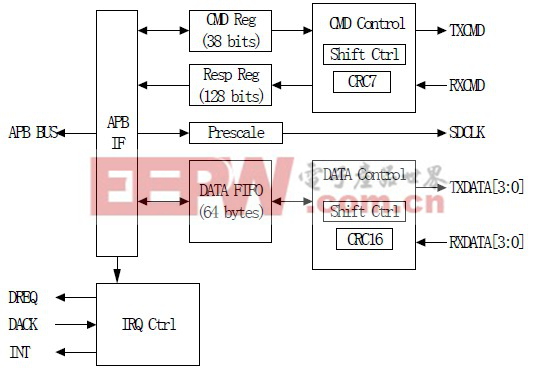

在整個SOC 中,我們這片TD 基帶芯片采用的是ARM926EJ-S 內核,系統架構為AMBA 總線。在設計中,將SD/MMC 卡控制器作為APB 的SLAVE 掛在APB 總線上,ARM 通過APB 總線來訪問和控制該模塊。本模塊主要分為接口模塊,CMD 控制模塊及DATA 控制模塊三部分。其結構框圖如圖1 所示。

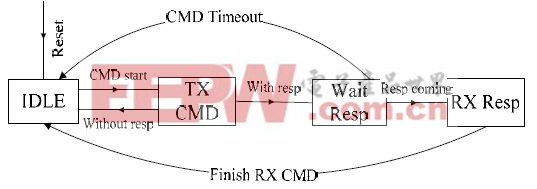

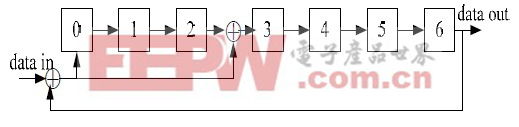

圖1 SD/MMC 控制器結構 接口模塊實現與ARM 的APB 總線相連接,通過該模塊,ARM 可以對相應寄存器進行讀寫,從而實現對本模塊和外部存儲卡的控制。其讀寫時序按照APB 總線讀寫時序,具體見文獻。 CMD 控制模塊主要發送和接收CMD 線上的信號。控制器發送給卡的命令長度固定為48bit,而從卡接收到的響應長度不固定,有短應答(48bit)和長應答(136bit)之分。 其中,包含CRC7 的子模塊,不管是命令還是響應,均要用到CRC 校驗。 DATA 控制模塊主要是通過RXDATA 數據線接收數據,并通過TXDATA 發送數據。主要的數據傳輸方式有兩種:比特流數據傳輸和多塊數據傳輸,另外,該控制器還支持無響應包數據傳輸。為確保傳輸的正確,包含了CRC16 校驗的子模塊。 2.2 CMD控制模塊的設計 由于SD/MMC 卡的操作命令不一致,在模塊中并沒有對命令作譯碼,而是通過軟件來設置命令的類型。單塊(signalblock data)讀數據命令(CMD17),寫數據命令(CMD24);多塊(mulTI-block data)讀數據命令(CMD18),寫數據命令(CMD25)等需要控制模塊根據SD_CMD_INDEX 寄存器的內容來發布相應的命令,并作不同的狀態轉換。CMD 控制模塊的狀態轉換圖如圖2 所示。 圖2 CMD 控制模塊的狀態轉換 2.3 DATA控制模塊的設計 本模塊主要功能是向卡發送數據和從卡讀取數據,另外,針對SD 卡該模塊可以通過DATA[3] 檢測卡是否插入,通過DATA[2]發送讀等待信號,通過DATA[1]接收卡送來的中斷信號以及通過DATA[0]來檢測卡是否處于忙狀態。 APB 總線上還有其他一些功能模塊,如SPI 接口控制器,CAMERA 控制器等,由于不能一直占有總線,在對卡進行讀寫的同時,來不及處理及時收到的數據或來不及獲取新的發送數據,所以我們采取數據緩存,添加一個64 bytes的FIFO。 控制器對卡進行讀操作時,需要先發送CMD9 命令,獲得卡的CSD 寄存器數據,其中包含了卡的數據長度,卡存儲容量,卡最大時鐘速度等。控制器可以持續進行數據讀取,直到向卡發送停止傳輸命令;或者讀取指定個數的數據塊。 讀數據過程中,如果卡檢測到錯誤,如超出范圍,地址對齊錯誤等,卡會停止數據發送,停在sending-data 狀態,控制器需要發送停止傳輸命令,此時,卡會將錯誤信息,通過響應返回給控制器。 控制器可以對卡持續進行寫數據操作,直到向卡發送停止傳輸命令;或者指定個數的數據塊寫完。寫數據過程中,如果卡檢測到錯誤,如寫保護,地址超出范圍,地址對齊錯誤等,卡會停止數據的接收,停在Receiving-data 狀態,控制器需要發送停止傳輸命令,此時卡會將錯誤信息,通過響應包返回給控制器。一個數據塊寫完后,卡需要一段時間將這塊數據寫到內部Flash 中,控制器需要查詢卡的狀態,等卡寫完數據后,才能發送下一個命令。 2.4 CRC的算法設計 在CMD控制模塊和DATA控制模塊中均用到CRC校驗。CMD控制模塊中用的是CRC7,其公式是G(x) = x7 + x3 + 1。實現其算法的邏輯圖如圖3。 圖3 CRC7 生成邏輯 在DATA 控制模塊中用的是CRC16,其公式是G(x) = x16+ x12 +x5 +1。算法邏輯圖同CRC7類試,這里我們不再贅述。 兩種校驗本質相同,后者精度更高,適應數據尤其是長數據的傳輸校驗。 3 功能驗證與綜合 使用Mentor 公司的ModelSim 軟件進行仿真,該軟件許可在PC、Solaris、HP-UX 或Linux 平臺上使用,支持VHDL或Verilog 硬件描述語言(HDL)仿真。它支持所有器件的行為級仿真和VHDL 或Verilog 仿真激勵。 為了測試設計的正確性,編寫了teSTbench 模塊,其中包括一個用HDL 描述的SD 卡的原型(使得控制器能夠對該卡進行操作),包括產生時鐘信號,輸出命令,讀寫的數據,產生的中斷等。下面以測試SDMMC 讀寫寄存器,發送命令接收響應,4 線塊數據(block data)傳輸等為例來說明: 對流傳輸,單塊,多塊數據等所有傳輸方式進行完仿真,利用目前業界最流行的綜合工具:SYNOPSYS公司的DesignCompiler對其綜合。經過對Script腳本約束的設定,通過DC將控制器的時序和面積進行優化,工作頻率滿足手機基帶芯片頻率125Mhz(最高可到200以上),面積在3萬門,比主流的4萬門有所降低,節省了面積。 最后采用Xilinx公司的xc4vlx200-10ff1513芯片進行FPGA驗證,測試結果表明該控制器可以對市面上主流SDMMC卡進行數據傳輸,符合整個SOC的要求。 4 結語 驗證結束后,利用中芯國際的0.13um的工藝庫對上面的設計進行封裝制造,就實現了最新的SD1.0和MMC3.31協議,并將其嵌入到ASIC中,使得TD終端具有外部擴展存儲性,節約用戶開銷。不僅如此,該控制器可作為一個成熟的IP核,移植到各種基于多媒體處理的ASIC芯片中去,其應用十分廣泛。 作者創新點:該IP核的設計,為TD-SCDMA終端基帶芯片以及類似手持SOC提供外接擴展存儲卡的功能,且具有廣泛的可靠移植性用于其他芯片中。

當滿足片選信號后,APB 總線對內部寄存器先進行配置,然后確定命令的發送,并附上CRC7 的校驗碼,最后接收響應和響應的CRC7 校驗碼。

評論