基于μC/OS-II的多窗口顯示屏控制器設計

摘要:多窗口顯示屏控制采用μC/OS-II實時操作系統(tǒng)的多任務管理運行模式,各窗口視頻數(shù)據(jù)由線程管理,Nios II 32位處理器作為顯示屏控制器硬件系統(tǒng)的核心,軟件系統(tǒng)控制多窗口任意顯示。在1片F(xiàn)PGA上實現(xiàn)顯示屏控制器的硬件系統(tǒng),利用SOPC Builder軟件定制系統(tǒng)所需的IP核,外擴存儲設備實現(xiàn)視頻數(shù)據(jù)的海量存儲,解決了FPGA內部資源相對不足的問題。通過重構視頻數(shù)據(jù),合理組織數(shù)據(jù)的存儲方式,解決視頻數(shù)據(jù)的灰度控制問題,減少數(shù)據(jù)處理過程,降低了控制系統(tǒng)的復雜度。

本文引用地址:http://www.j9360.com/article/149548.htm引言

LED大屏幕顯示屏是當今室外平面顯示的主流,其控制系統(tǒng)的技術發(fā)展也日趨成熟,控制系統(tǒng)按數(shù)據(jù)傳輸方式分為兩類:同步顯示和異步顯示。同步顯示控制系統(tǒng)即LED顯示屏和視頻數(shù)據(jù)源實時保持一致,視頻信號實時變化。異步顯示控制系統(tǒng)通過USB、通用串行接口、以太網等數(shù)據(jù)通信方式,更新大屏幕控制系統(tǒng)的視頻數(shù)據(jù)存儲區(qū)。數(shù)據(jù)更新由上位機控制,LED顯示屏的視頻信息變化由視頻數(shù)據(jù)存儲區(qū)的數(shù)據(jù)決定。在異步顯示系統(tǒng)中,可實現(xiàn)將顯示屏分為若干區(qū)域,不同的區(qū)域對應不同的存儲區(qū),數(shù)據(jù)更新時可以只更新其中的一個或幾個窗口。本設計采用嵌入式操作系統(tǒng)μC/OS-II的多線程控制方式,分別控制各個窗口的數(shù)據(jù)區(qū)域,實現(xiàn)單屏幕多窗口的任意位置顯示,使得顯示方式更加靈活方便。

1 系統(tǒng)總體設計

采用SOPC技術在FPGA上構建Nios II軟核作為LED顯示控制系統(tǒng)的處理器,實現(xiàn)32位的嵌入式系統(tǒng)操作。通過基于μC/OS-II的嵌入式操作系統(tǒng)的軟件設計,完成對DVI視頻顯示數(shù)據(jù)的接收和預處理。掃描電路接收視頻數(shù)據(jù)后進行存儲,同時將數(shù)據(jù)進行再組織并送往掃描屏。

1.1 系統(tǒng)硬件結構

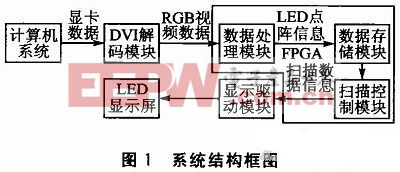

多窗口顯示屏控制系統(tǒng)的結構框圖如圖1所示。

計算機顯卡數(shù)據(jù)通過DVI接口將數(shù)據(jù)傳送給顯示屏控制系統(tǒng)的解碼電路部分,DVI解碼芯片將獲得的視頻數(shù)據(jù)解碼,得到RGB視頻數(shù)據(jù)和控制信號。控制信號中包含行掃描信號和場掃描信號,顯示屏控制系統(tǒng)根據(jù)場掃描信號判斷采集1幀視頻數(shù)據(jù)是否結束,并將視頻數(shù)據(jù)寫入發(fā)送系統(tǒng)的數(shù)據(jù)存儲器RAM進行緩存。FPGA從RAM存儲器中讀取數(shù)據(jù),將該數(shù)據(jù)按照灰度級分為8個區(qū)域模塊進行重新組織、轉換,然后通過移位串行時鐘送入LED顯示屏進行顯示。本系統(tǒng)的數(shù)據(jù)處理模塊、數(shù)據(jù)存儲模塊、掃描控制模塊3部分均在FPGA上實現(xiàn)。

1.2 軟件總體設計

全彩色LED大屏幕數(shù)據(jù)量大,本設計將顯示屏從邏輯上劃分為多個窗口,軟件部分基于μC/OS-II嵌入式操作系統(tǒng)編程實現(xiàn)。μC/OS-II操作系統(tǒng)的任務調度算法比較先進,在顯示系統(tǒng)中,可以將每個窗口的顯示操作都交給某個任務來執(zhí)行,這樣可以從很大程度上提高整個系統(tǒng)的運行速度和軟件的可靠性。

軟件基于Nios II IDE開發(fā)完成,應用程序基于μC/OS-II實時操作系統(tǒng)實現(xiàn)。軟件主要由2個任務和1個定時器中斷服務程序組成,任務間采用信號量的方式進行通信。計算機系統(tǒng)的顯卡數(shù)據(jù)經DVI解碼模塊解碼后得到RGB視頻數(shù)據(jù)。任務1接收RGB視頻信息,并對視頻信息進行濾波、數(shù)據(jù)的位組合、數(shù)據(jù)存儲區(qū)的重新組合等處理操作。任務2從內存中讀取數(shù)據(jù),并進行分析處理,把分析處理完的數(shù)據(jù)送往掃描控制模塊。利用μC/OS-II的實時性和多任務的特點,采用嵌入式文件系統(tǒng)進行數(shù)據(jù)管理。

2 控制器的硬件部分設計方案

2.1 視頻數(shù)據(jù)解碼模塊分析

采取從顯卡的DVI接口獲取數(shù)據(jù),經過視頻控制系統(tǒng)進行適當?shù)臄?shù)據(jù)變換,再發(fā)送到LED顯示屏上顯示。此模塊用來獲取視頻源數(shù)據(jù),完成對顯卡DVI接口傳輸?shù)腡MDS編碼數(shù)據(jù)的接收。通過TMDS解碼,實現(xiàn)對RGB視頻數(shù)據(jù)和像素時鐘CLOCK、像素有效信號DE、行同步信號HSYN、場同步信號VSYN、同步檢測信號SCDT等視頻顯示控制信號的恢復。

計算機顯卡輸出的DVI差分信號不能直接作為LED的掃描數(shù)據(jù)信號,需要經過解碼,將該信號恢復為數(shù)字視頻數(shù)據(jù)RED[70]、GREEN[70]、BLUE[70]等像素信息,還需要恢復控制信號,如行同步信號HSYNC、場同步信號VSYNC、數(shù)據(jù)使能信號DE和時鐘CLK等控制信息。需要一個解碼電路對DVI差分信號進行解碼,本設計采用TFP401A DVI解碼芯片實現(xiàn)該功能,解碼后的數(shù)據(jù)信息用于提供給LED屏控制器使用。

2.2 數(shù)據(jù)的存儲組織模塊分析

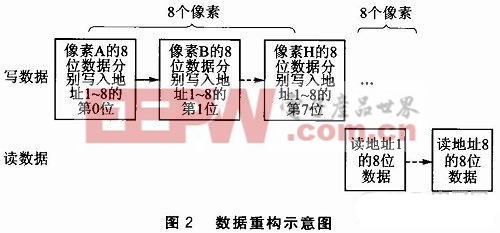

數(shù)據(jù)寫入SRAM存儲器中的組織方式有兩種:位平面法和組合像素法。位平面法是指像素的每一位分別存放在不同的存儲設備中;組合像素法是指畫面上每個像素的所有位均集中存放在單個存儲設備中。LED屏像素數(shù)據(jù)每一位的權值是不同的,高位的權值高,也就意味著高位為1時LED的點亮時間要長。根據(jù)兩種存儲結構的特點,對于LED屏,采用位平面結構有利于提高LED屏的顯示效果,從而更容易實現(xiàn)D/T(data to time)轉換。位平面法的數(shù)據(jù)需要重新組織,利用位平面結構有利于提高LED屏的顯示效果。數(shù)據(jù)重構示意圖如圖2所示。

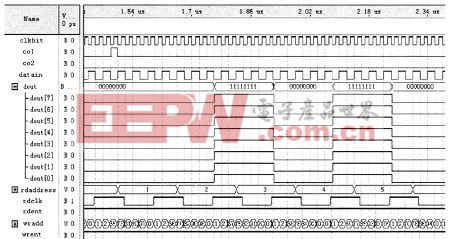

數(shù)據(jù)重構后,通過QuartusⅡ軟件編譯,得出如圖3所示仿真波形。其中,當col為1時,表示已寫完上面8個地址的數(shù)據(jù),此時讀地址計數(shù)器開始計數(shù)。datain為串行輸入數(shù)據(jù),dout為串行輸出數(shù)據(jù)。

圖3 數(shù)據(jù)重構模塊的仿真波形

評論