針對Motorola微處理器的BDM調試系統的設計

目前應用Motorola微處理器開發嵌入式系統時基本上都是使用Motorola公司提供的開發系統或者CodeWarrior公司的開發系統等付費昂貴的調試工具。最近由于Flash技術的發展,特別是一些CPU(如CPU12/16/32/32+,PowerPC5xx/8xx,ColdFire等)可以用JTAG口在背景模式下調試,故仿真器已可以省去。而且隨著BDM調試模式逐漸標準化,自制BDM調試工具變得越來越容易,特別是對于支持BDM調試模式的多種類型的CPU,自己設計的BDM調試系統只需少量的改動即可移植使用,而不必重復購買價格昂貴的調試開發系統,這樣做可以節省大量的成本。

本文引用地址:http://www.j9360.com/article/149202.htm1 BDM調試模式介紹

Motorola微處理器的調試模塊針對不同場合的應用分別提供了3種調試支持:實時跟蹤、BDM調試和實時調試。實時跟蹤是要求能夠跟蹤應用程序的動態執行路徑,這是實時系統的基本要求;在BDM調試方式下,處理器被停機,大量的命令可以被發送到處理器中訪問內存和寄存器,外部仿真系統使用一個三腳、串行的雙工通道與處理器通信;實時調試則可以不需要CPU停止運行,調試中斷允許實時系統執行一個惟一的服務例程,快速保存主要的寄存器和變量等上下文內容,并使系統立即返回到正常操作,外部的開發系統能訪問被保存的數據是因為硬件支持處理器和BDM初始化命令的一致性操作。

其中BDM調試模式為設計人員提供了一種低層次的調試手段,讓用戶能夠中斷CPU的運行,單步調試程序,讀取CPU的各個寄存器的內容,這些僅僅是通過向CPU發送幾個簡單的命令就可以實現,顯然,這樣使調試軟件的設計很簡單,通常自己就可以編寫。硬件調試卡的設計也非常簡單,關鍵是要滿足好通信時序關系和電平轉換要求。

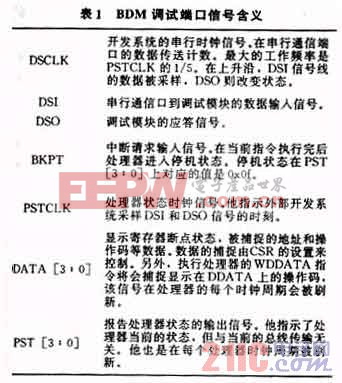

這幾種調試方式都共用26腳的BDM調試引腳信號,這些信號的定義如表1所示,BDM調試主要使用了DSCLK,DSI,DSO三種信號。

|

2 BDM調試系統的運行條件及其系統組成

(1)系統運行的限制條件

盡管許多BDM命令可以與處理器并行操作,但是要想安全可靠地使用BDM操作,最好的方法就是讓處理器停止運行。但是停機操作對于那些要求實時響應的應用程序的調試顯然不理想。但是由于實時跟蹤和實時調試模塊與BDM調試模塊引腳共用,所以升級和擴展BDM調試系統,可以很容易支持實時應用程序的調試。

(2)BDM調試系統組成

該系統主要由3個部分組成,如圖1所示。

|

BDM調試卡作用是完成從并口到BDM調試端口(信號定義如表1所示)的操作時序的轉換;BDM調試卡的驅動程序則是完成開發系統與待開發的嵌入式系統的通信過程處理,如合成一定格式的數據包、解釋接收到的應答數據或者微處理器的狀態數據等;BDM調試軟件則是功能軟件,完成讀寫指定位置的Flash或者SRAM數據、暫停、復位等功能。

值得注意的是,由于現在BDM調試模塊的標準化,調試卡和驅動程序在不同型號的CPU上將具有通用性,只是BDM調試軟件需要根據各種CPU對應的指令集來稍加修改即可復用。下面將以作者開發的一個針對Motorola公司的32位單片機MCF5272設計BDM調試系統的過程進行論述。

3 CodeFire系列處理器MCF5272的BDM調試系統的設計

3.1 BDM調試卡設計

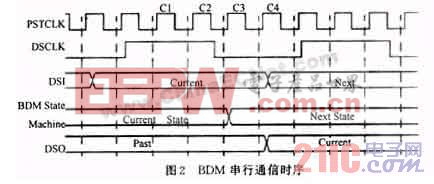

BDM接口的串行操作時序分析如圖2所示。從圖2中可以看出,在調試模塊的串行狀態機中所有的事件是基于處理器時鐘(PSTCLK)的上升沿的。DSCLK的頻率是PSTCLK的1/5,并且DSCLK的上升沿相對于PSTCLK的上升沿有一定的延時。這里的 DSCLK的作用類似于周期性的使能信號。每一次串行數據的傳輸可分為4個階段:C1,C2,C3和C4。在DSCLK的高電平期間,數據從DSI輸入,經過2個PSTCLK周期的同步(C1和C2)而被采樣,然后在DSCLK的低電平期間PSTCLK的第1個上升沿處(C3)來臨時BDM狀態機改變狀態,隨后在第2個PSTCLK上升沿(C4),DSI準備傳送新的數據,DSO上則輸出原來數據輸入相對應的應答數據。BDM狀態機在DSI上數據采樣檢測到的時候改變狀態,當所有的數據傳輸完畢,BDM狀態機的狀態也就不會有什么改變。

|

根據BDM端口的信號定義,不難看出這些信號都是單向的。其中要注意的是:PSTCLK是調試模塊從處理器中獲取的,而DSCLK則是外部的開發系統產生的。要實現從并口到BDM口的時序操作轉換,最簡單的方式是使并口工作在SPP端口模式下的4位組模式,在該模式下每次通過狀態端口的4個狀態位反向傳送半個字節,兩次傳輸完成向PC機傳送一個字節數據[1]。他的操作時序如圖3所示。

|

評論