編程嵌入式信號處理背板的開發設計

摘要:介紹了基于Virtex系列FPGA和TMS320C40DSP的可編程通用信號處理背板的設計和制作;并對Virtex系列FPGA的性能和特點進行了分析;同時還敘述了可編程通用信號處理背板的調試;最后給出了背板應用開發實例。

本文引用地址:http://www.j9360.com/article/149135.htm關鍵詞:Virtex系列現場可編程邏輯門陣列(FPGA)TMS320C40數字信號處理器(DSP)

現場可編程邏輯門陣列(FPGA)和高性能數字信號處理器(DSP)是高速信號處理領域兩大關鍵器件,FPGA和DSP的運算速度及并行處理效能成為制約高速信號處理應用的主要因素。FPGA以其設計靈活性及硬件高密度性在高速信號處理領域顯示出愈來愈重要的作用。Xilinx公司最新推出的Virtex系列FPGA。是一種采用5層0.22μmCMOS工藝的高性能、大容量現場可編程邏輯門陣列,其系統門密度高達100萬門,系統性能可達200MHz,可選擇配置為多種接口標準,內部含有豐富的布線資源,其SelectRAM和BlockRAM可靈活地配置為SRAM、FIFO、DPRAM、CAM等多種形式的存儲單元。Virtex系列FPGA含有極其豐富的I/O資源,可靈活地與TMS320C40DSP接口,與DSP配合可完成復雜的信號處理功能。C40DSP含有兩組外部總線資源和6個高速通信口,可方便地進行多DSP擴展,以提高系統信號處理的性能。

在對Virtex系列FPGA進行充分理解和研究的基礎上,結合對XC4000系列FPGA和DSP背板開發設計經驗,研制出了基于XCV200/300PQFP240和TMS320C40的可編程嵌入式高速信號處理背板。背板采用了針對系統需求自行開發的XPCI總線,背板可脫離實際應用系統進行獨立的面向應用的設計和調試,也可按照XPCI總線標準方便地嵌入到實際應用系統中,成為系統的一部分進行聯合調試。

對可編程嵌入式信號處理背板進行全面綜合測試的結果表明,背板性能達到了預期設計要求,工作狀態穩定。我們還針對實際應用開發了一些FPGA模塊和DSP程序。

1Virtex系列FPGA性能簡介

在前幾代FPGA開發的基礎上,Virtex系列FPGA結合了多種可編程系統的特征,采用了快速靈活的層次性互連布線資源和先進的處理技術,提供了高速度、大容量的邏輯解決方案,進一步縮短了數字信號處理系統的開發周期。與前幾代FPGA相比,Virtex系列FPGA的特性主要體現在以下幾個方面:

(1)更高的處理速度和更高的邏輯門密度。Virtex系列最大系統門數高達100萬門,系統性能可達200MHz,其中比較常用的幾個功能模塊性能如表1所示。

表1Virtex系列FPGA幾個常用功能模塊的性能

點擊看大圖

(2)更多可兼容的I/O接口標準。Virtex系列可兼容16種高性能接口標準,可直接與ZBTRAM器件接口,且其獨特的I/O分組方式可使多種不同電壓標準接口在同一片FPGA上實現。

(3)片內時鐘管理電路。Virtex系列內部包含4個靈活的延時鎖相環用于高級時鐘管理,可實現倍頻、分頻、鎖相等功能,此外還有4個主全局時鐘網絡和24個從本地時鐘網絡,以實現高速時鐘的傳輸。

(4)層次性存儲管理系統。Virtex系列內部查找單元可配置為16bit和32bitRAM、16bitDPRAM或16bit移位寄存器,其BlockRAM資源可配置為4kbitDPRAM或FIFO、CAM等存儲器件,且提供了高速外部RAM接口。

(5)更加靈活的系統結構。復雜的進位邏輯鏈提高了算術邏輯性能,復雜的乘法器支持,級聯鏈支持寬位輸入模塊,豐富的帶時鐘使能的寄存器和鎖存器,支持異步和同步復位及置位,支持IEEE1149.1邊界掃描邏輯。

(6)基于SRAM的在系統可重構技術。可無限次重復編程,包含主串、從串、SelectRAM和JTAG四種配置模式,支持部分重構。

2基于Virtex系列FPGA的可編程嵌入式信號處理背板的設計

由于對Virtex系列FPGA進行了充分理解和熟悉,我們研制了基于自行開發的XPCI總線的可編程嵌入式信號處理背板。由于Virtex系列FPGA內部結構相同,外部引腳兼容,只是在系統門數上有所區別,我們采用了XCV200PQ240-4作為可編程嵌入式信號處理背板的主處理芯片,與FPGA接口的DSP采用功能強大、接口靈活的TMS320C40DSP。背板中DSP的應用目的是對FPGA進行管理和控制、對FPGA處理結果進行分析、通過DSP軟件實現其他相關功能,以提高系統設計的靈活性。C40DSP具有兩組外部總線資源和6個高速通信口,能方便靈活地實現系統擴展。背板中FPGA可根據設計需要選擇不同規模的芯片。

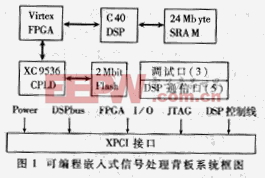

可編程嵌入式信號處理背板結構如圖1所示。

背板上主要包含1片XCV200PQ240FPGA、1片TMS320C40DSP、1片XC9536CPLD、1片EDI8L512SRAM(512K×32bit)、1片AT49020Flash2Mbit、DSP調試JTAG接口、FPGA調試X_Checker接口、CPLD調試JTAG接口、自行開發XPCI接口及5個獨立DSP通信口。背板所有器件除DSP外均采用貼片封裝、雙面裝焊,使得背板的尺寸較小(76mm×127mm×12mm),DSP外圍512K×32bitSRAM使得背板系統能夠滿足大部分應用程序的要求。2MbitFlash用于固化FPGA配置和DSP應用程序代碼。背板系統既可以獨立工作(Standalone方式),也可以通過XPCI總線嵌入系統工作(Plug_in方式)。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論