采用DSP與CPLD的三相五電平變頻器PWM脈沖發生器

1 引言

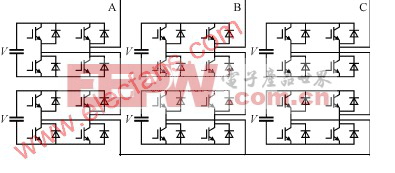

本文引用地址:http://www.j9360.com/article/148967.htm近年來,多電平變換器成為電力電子研究的熱點之一,它主要面向中壓大功率的應用場合。目前,有三種基本的多電平變換器拓撲結構[1]:①二極管箝位型;②飛跨電容型;③級聯型。

幾種拓撲結構各有其優缺點,但相對而言,級聯型多電平變頻器具有更獨特的優點,它的結構如圖1所示。它無需箝位二極管和電容,易于封裝,不存在電容電壓平衡問題,可采用砜關技術,以避免笨重耗能的阻容吸收電路1疚鬧饕介紹基于載波移相調制方法的級聯型三相五電平變頻器的PWM脈沖發生器的實現方法。

2 載波移相SPWM技術

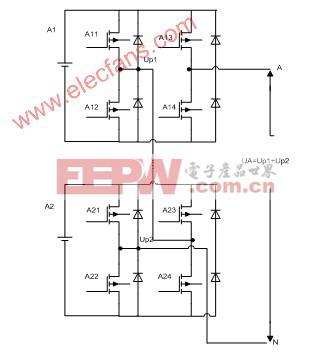

所謂移相式PWM技術就是將調制波和載波的頻率固定不變,調制波的相位也保持恒定,而只調整載波的相位,從而產生SPWM信號。將不同載波相位下的SPWM信號進行線性組合,達到消除諧波、提高輸出功率的目的。可以證明,當相移 時(α為同相的各單元的載波的移相角度,N 為級聯單元個數)[2],輸出諧波頻率增大到 2N 倍,更易于濾除。對于三相五電平變頻器,N=2,所以同相級聯兩單元的載波相差90度。如圖2所示,其中A11與

圖2三相五電平變頻器的A相

A14載波互差180度,A11與A21的載波互差90度,而A21與A24的載波互差180度。A1與A2串聯后的輸出電壓:

由(1)式可知UA不再包含2F±1次以下的諧波,僅包含2F±1以上的諧波。而當級聯數為N時,則NF±1以下的諧波均被濾去。

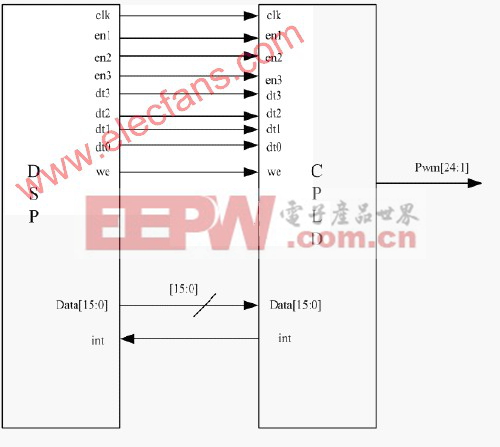

一個DSP只能產生12路PWM脈沖,而三相五電平變頻器需24路PWM脈沖,而用雙DSP輸出24路時存在同時性的問題,因而用復雜可編程邏輯器件CPLD來實現。當前,復雜可編程邏輯器件CPLD在現代數字電路設計中已成為不可或缺的器件,CPLD內部包含的邏輯門數從幾百至幾萬,具有可任意配置的幾百個寄存器和I/O口,并且開發周期短可靈活配置實現多種功能而無需改動硬件電路。

pwm相關文章:pwm原理

評論