采用DAC芯片AD9248和CY7C09449的PCI高速數據采集方案

0 引言

本文引用地址:http://www.j9360.com/article/148813.htm數據采集向高精度和高速度兩個方向發展。高精度數據采集依賴于A/D器件的精度,高速度數據采集不僅依賴于A/D器件的速度還依賴于數據采集系統的設計。高速數據采集按是否可連續采集而可以分為兩類。第一類是在一段時間內的高速數據采集,采集數據的時間長度取決于存放數據的RAM存儲器的空間大小;另外一種是可以連續地高速數據采集,采集的數據被存放在大容量的存儲器上,一般為硬盤,這種采集的速度相對較小。本文提出屬于第一類的PCI接口高速數據采集方案,可以實現高達80Mb/s的數據采集速度。

1 硬件結構

高速數據采集卡的硬件結構見圖1。

采集系統使用AD9248 DAC芯片,可以同時對兩路模擬信號進行模數轉換,每路輸入可以選擇差分輸入或單端輸入。它最大的采樣率可達65MS/s,采樣精度為14bit。數據傳輸使用了CY7C09449集成芯片,它實現局部總線和PCI總線之間的數據傳輸。一片FPGA將CY7C09449和AD-9248連接起來。FPGA的作用有兩個,其一是控制A/D芯片實現數據轉換,其二是和PCI接口芯片交互,實現數據傳輸。

硬件設計上,CY7C09449和PCI總線是無縫連接,CY7C09449的局部總線和FPGA相連,AD9248的數據線及控制線和FPGA相連。軟件設計包括FPGA器件的邏輯設計、高速數據采集卡在WindowsXP下的驅動程序設計和應用軟件設計。本文主要介紹高速數據采集卡的軟件設計。

2 數據采集過程

CY7C09449是美國Cypress公司生產的一款PCI接口控制芯片,支持PCI2.O協議,可以作為PCI總線的主設備也可以作為PCI總線的從設備。CY7C09449的局部總線可以和多種常用的微處理器直接相連。它內部包含的128kbit的雙端口SRAM共享存儲區可以從PCI總線訪問也可以從局部總線訪問,這是它最主要的資源。它內部包含的一些配置寄存器可以從PCI總線訪問也可以從局部總線訪問。在PCI總線上,CY7C09449可以處于從設備的地位,接收主機對它的配置寄存器或共享存儲區的訪問。在PCI總線上,CY7C09449也可以處于主設備地位,主動發起數據傳輸,將數據傳出或存入共享存儲區。它能夠產生任何32位PCI總線地址,可以發起PCI總線的突發傳輸。在局部總線上,CY7C09449處于從屬的地位,微處理器控制著對它訪問的主動權。CY7C09449的局部總線本質上是同步傳輸接口,可以支持突發傳輸。TMS320VC33處理器通過配置CY7C09449內部寄存器使其與SCY7C09449的局部總線相連接,并兼容TMS320VC33的異步訪問方式。

數據采集的過程由主機發起。主機的應用程序向驅動程序請求數據采集,驅動程序通過寫入CY7C09449的主機控制狀態寄存器0bit使引腳RSOUTD的狀態由低電平到高電平轉換,FPGA根據此信號來啟動一次數據采集。FPGA從A/D讀取數據,然后寫入CY7C09449的SRAM中。SRAM的大小為4k的雙字,FPGA把它分為2個2k雙字的塊,循環交替使用。FPGA每寫完一個塊就通過CY7C09449的引腳IRQ IN向主機請求一次中斷。主機的驅動程序在中斷服務程序中通過寫入CY7C09449的DMA局部基地址寄存器、DMA主機物理基地址寄存器、DMA長度寄存器來配置數據傳輸的源地址、目的地址、數據長度,然后再寫入CY7C09449的DMA控制寄存器來啟動DMA傳輸。這樣直到本次所有的數據采集完畢,FPGA停止數據的讀取處于等待狀態。主機的中斷服務程序在收到最后一塊數據后向應用程序發送一個消息,告知本次數據采集完成。應用程序這時就可以處理采集到的數據或將數據存在硬盤中。

3 FPGA的邏輯設計

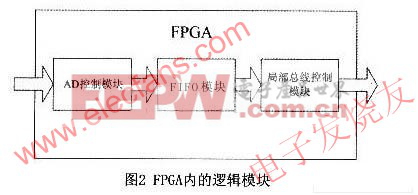

FPGA器件要實現的功能是從A/D器件讀取數據,然后通過局部總線將數據傳送給CY7C09449內部的雙端口SRAM。對FPGA的邏輯編程是在Quatus6.0下進行的。頂層邏輯設計使用原理圖設計方法,把FPGA的邏輯分為3個模塊,每個模塊內部邏輯使用文本設計方法,使用VHDL語言編程。FPGA內的邏輯模塊如圖2所示。

A/D控制模塊產生A/D器件的控制信號,從A/D讀取數據,然后寫入FIFO。AD控制模塊的功能相對比較簡單,也比較容易實現。

因為在數據采集的過程中A/D采樣速度數據是固定的,但是數據傳輸有時速度很快而有時因為等待出現短時的阻塞。所以必須要有FIFO來緩沖采集的數據。FIFO模塊是用Quatus6.0的向導生成的,只需要設定有關參數即可。FIFO的寫入和讀取使用同步接口邏輯,FIFO的存儲寬度是32 位,其深度是512。

局部總線控制模塊從FIFO中讀取數據然后寫入CY7C09449的SRAM中。CY7C09449的局部總線支持同步數據傳輸,雖然它也兼容異步數據傳輸,但FPGA的局部總線控制模塊選用了同步數據傳輸邏輯,因為這樣可以獲得更高的數據傳輸速度。CY7C09449的局部總線支持最高的時鐘速度是50MHz,一次同步的突發數據傳輸在給出讀或寫的起始地址之后,每個時鐘周期可以傳送一次數據。CY7C09449局部總線的數據總線寬度是32位,這使得局部總線的最高傳輸速度達200Mb/s。

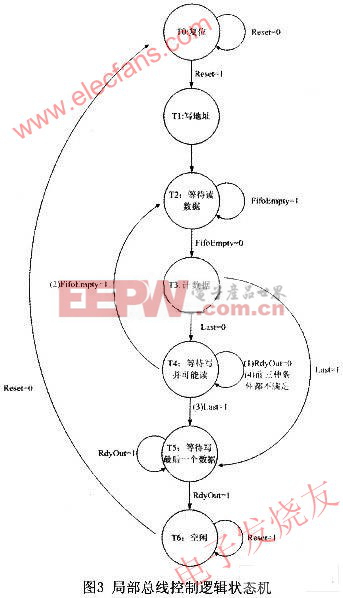

在CY7C09449的局部總線上,FPGA處于類似于微處理器的地位,控制著局部總線數據傳輸的主動權。FPGA的邏輯設計中,局部總線控制模塊的邏輯設計是獲得高速數據傳輸的關鍵。同步數據傳輸要比異步數據傳輸的邏輯復雜得多。在局部總線控制模塊的邏輯設計中使用了狀態機,其設計的關鍵在于狀態機的狀態的定義和在各種條件下狀態的轉換。為了簡單起見這里不對多塊數據傳輸控制、中斷信號產生邏輯作討論而只介紹傳送一個數據塊的邏輯。

狀態機共定義了7個狀態,各種狀態的轉換關系見圖3。

評論