一種基于ARM和FPGA的可重構MAC協議設計

(1)若MAC_flag為false時,表明信道空閑,此時進入(2);若MAC_flag為true,則說明現在信道已被占用,此時不管節點已經處于什么狀態都會進入第七步,除了正在發送數據的節點,由于正在發送的節點是不可能監聽信道的,而且也無法接收其他節點的數據,載波偵聽機制在這種狀態下是失效的,因此不會出現正在發送數據的節點從發送狀態突然變為接收狀態。

(2)執行幀間間隔進程,遞減IFS_time大小,直到為0就進入(3)。IFS_time的初始值為DIFS。

(3)退避進程。退避時間的大小主要是由ARM提供,當節點經歷了一個時隙時間,退避時隙數減1,但當節點沒有完全經歷一個時隙時間,退避時隙數就不會變化。退避進程結束后就會進入(4)。

(4)判斷發送類型,設計中發送類型Tx_tpye的初始值為1。若Tx_tpye為0,則為節點發送ACK,根據接收到的數據幀中的源/目的節點號以及序列號等組裝回復發送節點ACK,并初始化IFS_time和Backoff_time以備節點發送數據幀使用,同時設置NAV_flag為true,更新NAV_time的值,繼續虛擬載波偵聽,避免出現發送ACK的節點會優先占用信道的情況;若Tx_tpye不為0,則表明節點可以開始發送數據幀,轉入(5)。

(5)發送數據幀前首先判斷是否超過最大允許發送的時間,若超過了就丟棄該數據幀,將IFS_time設置為EIFS,Backof_time初始化,超時計時器停止;若沒有超過最大允許發送時間,則節點正式發送數據幀,并啟動單次超時計時,發送完畢后就等待ACK,此時進入(6)。

(6)在等待ACK到來的同時判斷是否超時單次允許發送的時間,若超過了,則重傳次數遞加;然后判斷是否超過重傳門限,如果超過了門限,則丟棄該數據幀;如果沒有超過,則將IFS_time設置為EIFS,而且還需要ARM的隨機退避算法根據重傳次數重新給一個退避時隙數,同時修改數據幀中的重傳位以便接收節點識別。

(7)保存當前退避進程中的Backoff_time和剛剛結束的幀間間隔的大小IFS_time,接收MAC幀并解析其中相關的數據,為后續的組裝ACK做準備,然后進入(8),同時將NAV_flag設置為true,保證MAC層能處理完數據。

(8)校驗接收到的MAC幀是否正確,若不正確,則將IFS_time設置為EIFS,NAV_flag設置為false,NAV_time設置為0,這樣節點就進入執行幀間間隔進程。若校驗正確,則進入(9)。

(9)將FPGA解析出來的目的節點號與本節點的比較,判斷是否是發送給本節點的。如果不是發送給本節點的,那么就再比較本節點現在的NAV_time值是否大于接收到的MAC幀內的NAV,若大于則本節點繼續按照現有的NAV_time值執行下去;若小于接收到的MAC幀內的NAV,則使用MAC幀內的NAV來更新本節點的NAV_time值,然后以最新的NAV_time值遞減下去直到為0,虛擬載波偵聽顯示空閑。但是在執行NAV_time遞減過程中隨時都有可能收到新MAC幀,而且也不是發送給本節點的,照樣要執行本步驟,并不是等到NAV_time變為0后再更新。如果是發送給本節點的,則會進入(10)。

(10)若節點接收到的是數據幀。即Rx_type為1,FPGA將接收到的數據幀上傳ARM;同時將IFS_time更新為SIFS,Backoff_time設置為0,這樣使得接收到數據幀到發送ACK之間的時間間隔為SIFS,并將Tx_tpye設置為0,NAV_flag變為false,進入(2),開始準備發送ACK。如果Rx_type為0,則節點接收到的是ACK,說明一次數據收發過程結束,節點將初始化相關參數,計時停止等,FPGA釋放空間,表明該數據幀已發送成功。

3 仿真驗證

基于CSMA/CA的MAC協議的實現關鍵在于各個節點對各種情況的處理,因此對一個節點協議功能的仿真驗證也能說明設計的正確性。本設計中FPGA部分的設計是重點,所以使用ModelSim進行仿真觀察節點FPGA的處理過程。

3.1 信道競爭過程

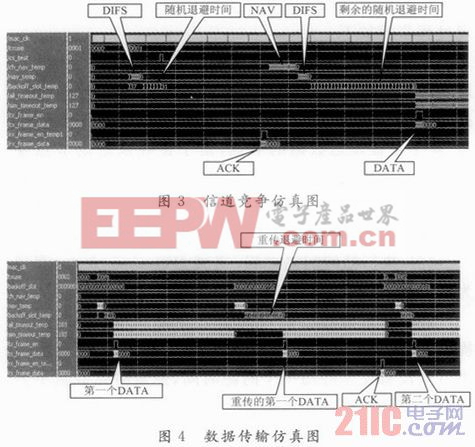

基于CSMA/CA的MAC協議中各個節點也不知道自身周圍的節點情況,因此節點競爭信道時隨時都可能檢測到信道已被占用。圖3給出了節點在退避過程中檢測到物理載波偵聽變為忙,立刻停止退避進程,將此時的退避時隙數掛起,即退避時隙數保留為31。待到信道重新空閑超過幀間間隔DIFS后,將以保留的退避時隙數繼續進行退避進程,變為0后開始發送數據幀。在圖中還可以看到節點收到正確的ACK后,更新NAV的過程。從仿真圖的執行流程可以說明所設計的MAC協議滿足載波偵聽機制、幀間間隔、隨機退避的功能要求。本文引用地址:http://www.j9360.com/article/148811.htm

3.2 數據傳輸過程

從圖4中可以觀察到節點發送第一個數據幀后,超時計數器開始計時,但在規定時間內沒有收到ACK,則重傳數據幀,重傳退避的時間是重新賦值的,并且幀間間隔不再是DIFS,而是EIFS;當節點接收到正確的ACK后,開始發送新的數據幀。說明了所設計的MAC協議能夠實現確認重傳機制。

4 結語

在以ARM和FPGA為主的硬件結構上,設計與實現了基于CSMA/CA的MAC協議,該協議具有載波偵聽機制、隨機退避、確認重傳等功能。經過仿真測試,驗證了所設計MAC協議的可行性。

評論