嵌入式系統的除錯策略

嵌入式系統除錯的工作量,可望占了嵌入式軟體專案工作量的一半以上。了解硬體除錯功能以及它們所能解決的問題,是選擇正確的晶片、建立除錯系統以及提高生產效率的關鍵。

本文引用地址:http://www.j9360.com/article/148126.htm很多人都相信臭蟲(bug)此一用詞起源于海軍少將 Grace Murray Hopper。但事實上,沒人知道這種用法的真正來源,它可能可以回溯到 Thomas A Edison,或甚至更早。美國海軍后備役軍官 Hopper 在 1945 年 9 月 9 日于哈佛大學對 Mark II Aiken 繼電計算器( Relay Calculator)進行測試時,于短路的 Panel F #70 號繼電器處發現了一雙臭蟲。她把這只臭蟲拿掉后(就是對電腦進行除臭蟲(debugging)),就解決了這臺機器不定時關機的故障(參考文獻 1)。雖然這個早期的例子指的是從系統硬體中去除臭蟲,但今天debugging這個詞是指發現一個程式的問題,并去掉缺陷代碼(defective code)的過程。這些問題包括任何與原始意向的差異,而去掉缺陷代碼的做法則遠優于增加糾正代碼(correction code)。理想情況下,在任何時間都可以獲得所有的特性(如系統的R流排與暫存器值),供監控與修改。但隨著 IC 轉向 SoC,可存取性(accessibility)就變得更加困難了。

對硬體除錯,是要盡可能地可以存取到嵌入式系統內部資源,這可以透過觀察系統的特性,如 CPU 狀態和 PC 值,或修改系統的參數。在嵌入式系統設計的早期可以用簡單技術進行除錯,如記錄(logging)與監控,或者對多核心 SoC而言,可以采用最新開發的方法,如跟蹤、緩衡記憶體除錯(cache debugging)和交叉觸發(cross-triggering)等。本文的重點不是在如何編寫代碼或為代碼除錯,而是描述現在可用的嵌入式硬體硅智財權(intellectual property ,IP),以及該 IP 能解決哪方面的除錯問題。

記錄與監控

最古老也是最常用的除錯方法就是在代碼中增加一些列印敘述(print statement),它可以顯示軟體某個部分的執行資訊,并提供暫存器和變數的實際值。這可能是一年級學生練習hello world的一種延續,該程式會在熒幕上顯示這兩個詞,用于表示程式能夠運行,以及執行到了某個點。列印敘述(或 printf 語句)只是記錄的一種變型,它是用處理器將重要資訊寫入一個管道(pipe),作為外部跟蹤的過程。所使用的管道將視系統而訂,在 printf 情況下,管道是標準的輸出(熒幕),但它也可以是 UART、USB,甚至是通用 I/O。

當你需要用一種對程式設計工程師有意義的方式,組織各個部分資訊時(例如提供感測器資訊或狀態機的轉換),采用記錄的方法是很有價值的。可以用記錄工具來分析記錄的資訊,并產生一個后處理資料庫。必須小心使用記錄功能才能獲得高效率。例如,記錄資訊應使用關鍵字開頭,如警告、錯誤或除錯等,并應能識別出資訊的建立者。應將記錄功能劃分為一小組檔案,以便于維護,并提供時間戳資訊。不幸的是,記錄是一種侵入性的方法,它會修改軟體的即時狀態,因而不同于最終應用。

除錯監控器是另一種常見的除錯工具,它與運行在 CPU 記憶體中的目標代碼一起工作(參考文獻 2 和參考文獻 3)。除錯器運行在一臺主機上,它透過一個專用的埠發送指令和接收響應,從而達到與監控器通信的目的。可以將 Linux 上的 gdbserver 程式當作一個除錯監控器,不過它比早期的 ROM 監控器更復雜

(圖 1)。

當使用者希望在某條指令處設置一個中斷點時,gdbserver 會保存該指令,而用一個系統呼叫(system call)來替代它。Gdbserver 然后用 Linux 的 ptrace 程式獲得所有進行系統呼叫的應用程式資訊。接著,當發生系統呼叫而⒍中斷點時,gdbserver 可以取得對被除錯應用的控制。除錯器運行在一臺主控機上,透過串列埠或乙太網路連接到目標物件(參考文獻 4)。監控器的方法既便宜又實用,但也有一些缺點,例如需要在進行任何除錯前載入代碼,并可能與應用軟體相互影響。如果代碼位于快閃記憶體中就不能使用監控器軟體,因為要插入軟體中斷點就需要修補應用軟體。

內電路模擬

內電路模擬器(in-circuit emulator ,ICE)是第一種以硬體為基礎的除錯技術,它是所除錯處理器的一個版本。ICE 通常使用一顆現場可編程閘陣列(field-programmable gate array,FPGA)。FPGA 外合(bond out)其內部R流排和狀態信號,而讓使用者可以使用它們(圖 2)。

ICE 提供的除錯功能多于 ROM 監控器。使用 ICE 時,必須用一個連接到 ICE 盒的連接替換待除錯電路板上的處理器。一個運行并模擬除錯器功能的主機控制這個 ICE 盒。ICE 的主要局限性之一是它的價格昂貴。另外,雖然這個方法很適合簡單的處理器,但現代 SoC 有更高的復雜性、整合度和頻率,因此 IC 供應商難以為現代處理器提供 ICE 版本。

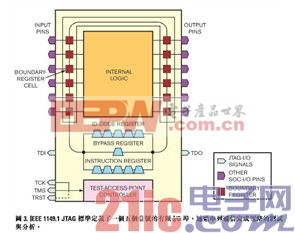

一些歐洲公司在1985 年成立了聯合測試活動組(Joint Test Action Group,JTAG),這個聯盟嘗試要解決測試半導體 IC 的各種問題。它們為 IC 的邊界掃描測試建立了 IEEE 1149.1 標準,并在 1990 年公布了此一標準(參考文獻 5 和 圖 3)。

JTAG 標準定義了一個有限的 I/O JTAG 埠,有多達五個信號,透過串列通信完成電路的測試與分析:測試時(test clock,TCK)、測試模式選擇(test-mode select,TMS)、可選的測試重定(test reset, TRST)、測試資料登錄(test-data in ,TDI)和 測試資料輸出(test-data out,TDO)。

IEEE 將 JTAG 硬體建立在一個 16 態的有限狀態(finite-state)機上,并由 TMS 信號控制。TCK的上升沿時(rising- edge clock)X取到此一 TMS 信號。資料資訊在TDI 墊(TDI pad)移入,并在TDO 墊移出。最后用 TRST 來對設計重新設定。IC 的每個墊都可以增加掃描暫存器,并將它們內部連接起來構成一個邊界掃描鏈。可以透過 TDI/TDO 和 JTAG 命令將此鏈移入和移出,以測試電路板上的外部連接,測試 IC 內部的邏輯連接,X取 IC 墊的值,并將 JTAG 置于旁路模式。JTAG 提供了低成本的u造測試功能,并成為最常用的測試方法。但是,由于它有易于使用、高可用性和低成本實現的特點,設計者經常會把 JTAG 當作除錯埠,以存取片上的除錯資源(參考文獻 6)。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論