在基帶處理中使用串行RapidIO協議進行DSP互連

摘 要:本文分析了傳統的多個DSP 的各種互聯的方法,提出將串行RapidIO 協議,這種基于開關的、點對點的互連方法作為基帶數據處理中的互連方案,可以減少成本,并且提供高帶寬下低延時的雙向通信。然后結合基站基帶處理,這種方案具有很大的靈活性,最后總結了使用這種互連方案的好處。

本文引用地址:http://www.j9360.com/article/148093.htm目前,在通信系統中,比如在 VoIP 網關和無線基站的系統中,語音和數據都在急劇增加,系統的處理能力也要極大地增加,因此單個DSP 已經不能滿足越來越多的需求,需要把多個DSP 互聯成DSP 簇來增加對更多數據的更快處理能力。DSP 的互連有很多種,不同的應用場合可以使用不同的DSP 互聯。比如基于總線的多DSP 結構復雜,而且因為共享總線造成總線帶寬,降低系統整體的效率,總線瓶頸的限制將凸顯出來;通過HPI 接口-可以提供DSP 之間的互聯,但是數據傳輸速率有限,數據傳輸有時會成為系統處理能力提高的瓶頸,造成系統整體效率的降低;多通道緩沖串口MCBSP-數據傳輸帶寬有限,他們都不適合多DSP 之間的高速數據傳輸。DSP 簇需要通過一種特殊的方式互聯,以支持更高的帶寬,同時進行低延時的雙線通信。可以通過專用的互聯芯片來實現多DSP 互聯方案,這樣,連接上不會復雜,而且具有靈活性和高速傳輸的特點。在無線基站中,如果利用RapidIO協議進行DSP 互連則可以大大提高運算效率。而且目前芯片的廠家已經生產出支持串行RapidIO 接口的芯片,使得DSP 之間高速互聯成成為可能。

1. 系統介紹

1.1 串行RapidIO

RapidIO 商業聯盟組織2001 年提出了針對多處理器互連的RapidIO 協議。RapidIO 協議是一個點對點的包交換協議, 有物理層、運輸層和邏輯層3 層結構。邏輯層為RapidIO 節點的交易, 定義了所有的包格式:運輸層為RapidIO 數據包提供了路由和尋址的功能;物理層提供了設備接口的電氣特性說明此外, 協議還提供了流量控制、差錯控制等功能。對于采用較少連線的長距離傳輸以及背板傳輸,由于RapidIO 物理層采用Lvds 傳輸和高速串行收發器技術,在每個方向上支持高達10-Gbps 的數據吞吐量,可用在圖像和信號處理、高帶寬存儲器接口等領域中。

1.2 DSP 之間通過串行RapidIO 進行互連

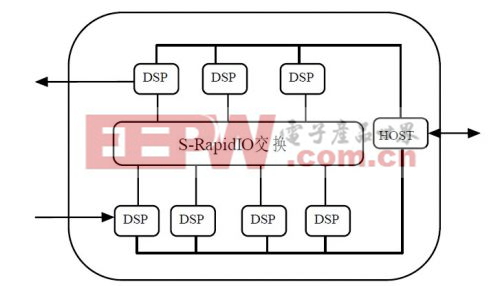

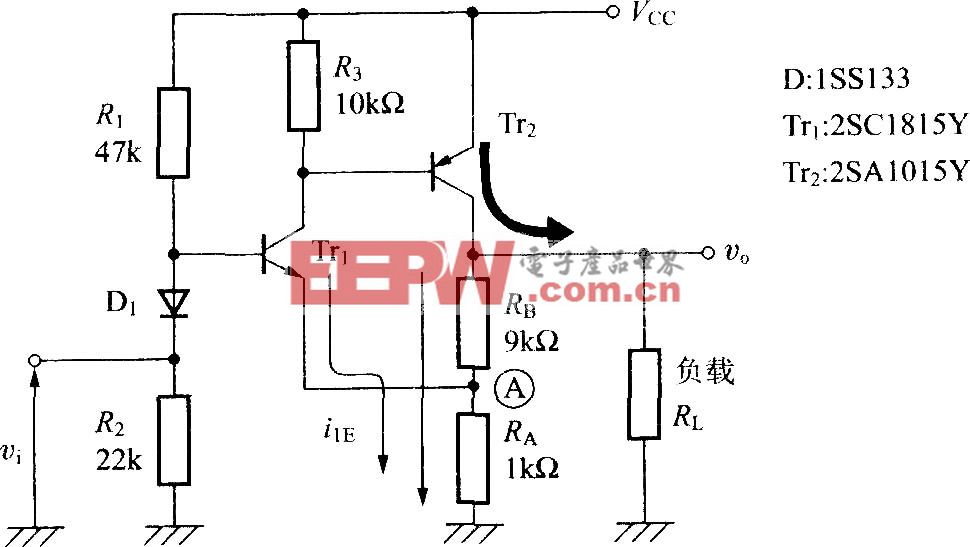

如果 DSP 簇的互連使用串行RapidIO 協議,可以大大提高吞吐量。如圖1 所示:

圖 1 一種初步的互連方案

可以看出,幾個DSP 通過這種方法進行互連,利用兩個DSP 分別從外部收集未處理的數據并將處理好的數據送出,在幾個DSP 內部利用串行RapidIO 協議,數據在幾個DSP 之間高速運轉,正是因為RapidIO 這種基于點到點的傳輸特性才能使得高速傳輸的實現。另外,還可以通過一個外部的主機hoST 來實現控制這幾個DSP 的一些功能,比如在某種場合可以只運行某個DSP 進行特殊運算,那么其他的DSP 則處于不工作的狀態。這種DSP 之間使用串行RapidIO 互連有很多優點:

1、RapidIO 協議分為三層,所有DSP 可以集中處理碼元速率和符號速率。

2、擁有可以升級的交織查找表,可以平衡幾個 DSP 的工作量。

3、這種點到點的開關互連可以滿足更高更復雜的要求,比如多用戶檢測等等。

4、協議中四種優先級設定,允許高優先級的優先通信。

5、RapidIO 中的數據流,可以選擇第六種數據類型,允許數據傳輸具有更小的包頭。

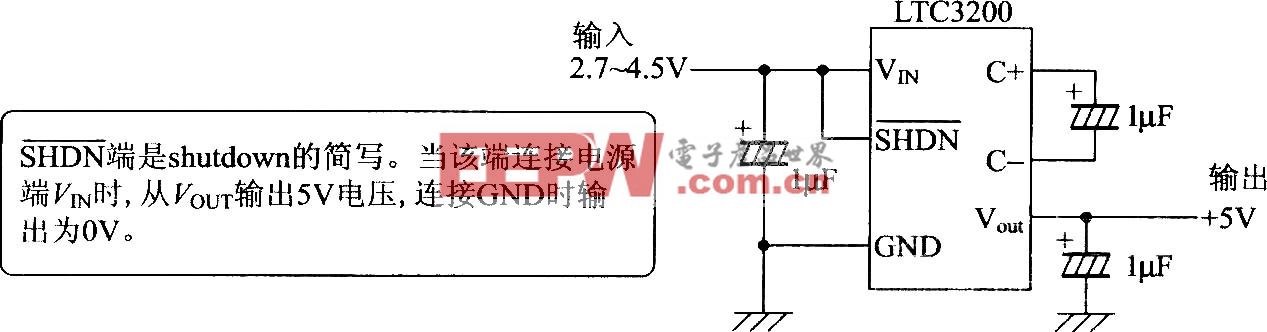

1.3 無線傳輸系統基帶部分

在無線傳輸中,模擬的用戶數據經過射頻模塊進行模擬的轉換,發送到基站的基帶板接收,運行一系列的運算規則進行調制解調來分析用戶數據。基帶子系統完成信道解擴解調、編譯碼、擴頻調制的功能。基帶子系統對上行基帶數據進行解調,包括相關、信道估計、頻率跟蹤和RAKE 合并等,然后經過譯碼處理、FP 處理傳遞給傳輸子系統。而在下行鏈路中,基帶子系統接收到來自傳輸子系統的FP 包,根據要求完成編碼,包括TB 塊CRC 校驗和碼塊分段、信道編碼、速率匹配、交織、傳輸信道復用與物理信道映射等,將下行數據發送到中頻子系統。其中,互相關、信道估計和多用戶檢測等通常都是用ASIC 和FPGA 來實現的,Viterbi 譯碼和turbo 譯碼等通常都是用DSP 實現的。如圖2 所示:

圖 2 基站基帶處理板簡化框圖

傳統的 ASIC/FPGA 構成的處理器,沒有對等網絡的要求,對語音、數據進行固定分配,處理效率比較低。因此可以考慮用DSP 來實現,但是單個DSP 只有一個內核,它的處理能力非常有限,處理數據的速度不及FPGA.如果多個多核協作進行并行計算,則可以成倍提高DSP 的處理能力,因此可以考慮多個DSP 互連。多個DSP 通過高速協議互連構成的DSP簇能夠很靈活地實現多種功能,他們之間通過軟件編程,可以非常靈活地適應更高復雜的要求,并且使對等網絡通信成為可能,具有更高的吞吐量。

由于這種模塊只有 DSP 在運算,需要進行負載均衡,對于處理鏈中的DSP 簇,需要給每個DSP 分配不同的算法模塊。因為需要更高的數據速率并且需要更復雜的多用戶運算,進行信道估計和檢測,需要用多個DSP 對這些運算進行負載均衡,從而去實現更大的算法模塊。比如說可以給每個DSP 相同的算法,也可以讓每個DSP 本身成為一個獨立的算法模塊,這些都是非常靈活的。

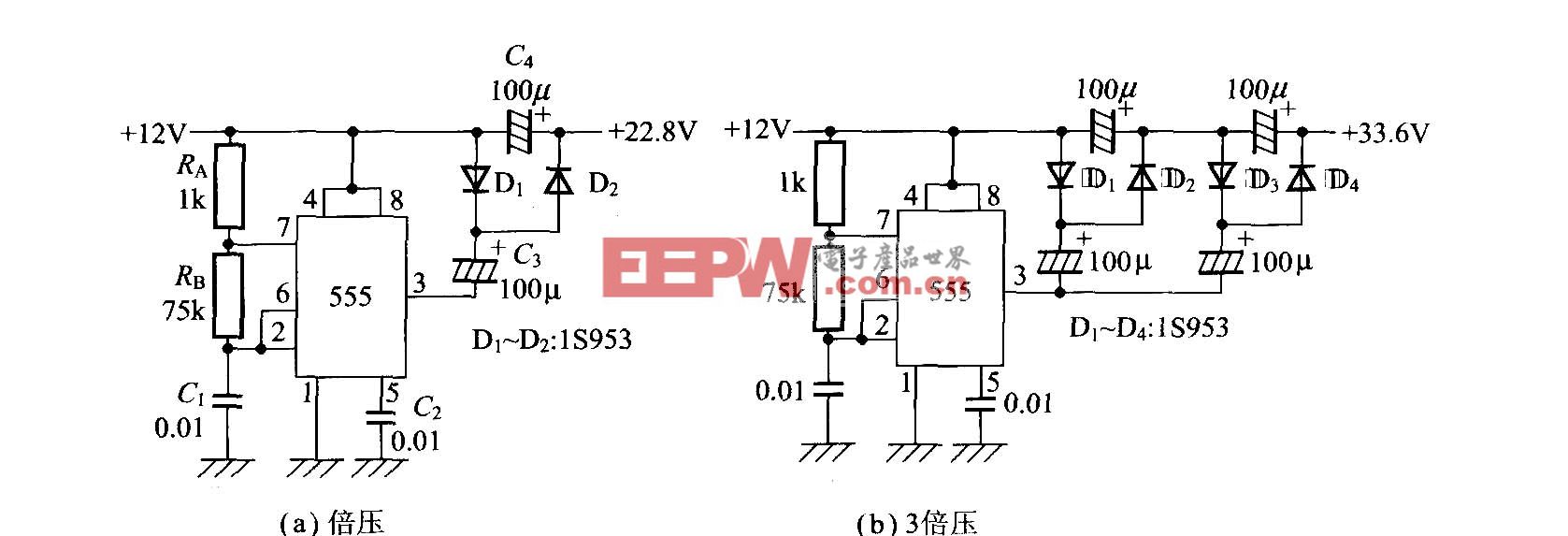

2. 系統的具體實現

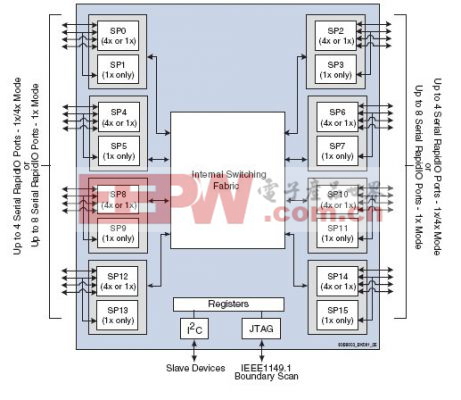

DSP 之間通過RapidIO 協議進行通信的實現方法,目前可以通過FPGA 實現,FPGA 作為DSP 節點本地互連網絡協處理器,采用了分層結構,包括DSP 接口層、RapidIO 的邏輯層、運輸層和物理層[4].DSP 通過外部存儲器接口( EMIF) 和FPGA 相連。但是這種方法需要在FPGA 內部進行比較復雜的互連。目前,TUNDRA 公司推出了一款專門的串行RapidIO芯片--TSI568A.

圖 3 Tsi568a 的內部結構。

評論