基于FPGA的二取二總線數據比較器

摘要:基于FPGA的二取二總線數據比較器實現聯鎖邏輯運算的兩塊CPU板總線數據的實時校核。在兩條總線數據比較一致且總線數據的CRC校核通過時兩個FPGA分別輸出互為反相的動態脈沖,板上驅動電路輸出信號控制板外供電繼電器對聯鎖系統驅動單元供電,否則通過停止輸出動態脈沖在50ms內切斷供電繼電器。出現校核錯時FPGA將比較不一致的兩個數據及在對應數據包中的位置等信息反饋給對應CPU板,便于故障分析。通過監測回讀信號實現板上驅動電路的實時檢測,在驅動電路出現硬件故障時可導向安全。該比較器遵循EN50128,EN50129和EN50126標準流程開發,已通過歐標SIL4級安全認證。

本文引用地址:http://www.j9360.com/article/134005.htm背景

高速鐵路的發展對信號設備性能、穩定性、安全性提出了更高的要求。其中安全性中故障導向安全是設備設計開發中首先要遵循的原則,盡早發現,盡早防范是信號設備安全設計中需考慮的問題。CPU作為控制設備中核心單元一旦運算出錯很可能會導致災難性后果。二取二系統中雙CPU校核可有效避免單CPU故障引發的災難性后果。雙CPU校核實現方式包括軟件比較和硬件比較。軟件比較指CPU通過通信等方式得到對方的數據后各自進行比較,如果比較不一致則通過控制其他外圍單元切斷輸出單元的對外輸出使系統導向安全。硬件比較指通過第三方硬件實現兩個CPU總線數據的實時比較,不一致時通過第三方硬件可直接切斷輸出單元的供電,無需CPU參與任何控制(此時故障的CPU可能已不能正常控制其它外圍單元)。現場可編程邏輯陣列(Field Programmable Gate Assay,FPGA)通過硬件描述語言進行編程,可完成大規模實時邏輯處理和高速總線接口處理。總線校核需要進行大數據量、快速邏輯處理因此很容易發揮其長處。二取二架構的控制系統安全性高于單機系統因而在鐵路系統中得到廣泛應用。面向二取二架構的雙CPU總線數據比較,我們開發了基于FPGA二取二總線數據比較器,比較器在CPU每個控制周期內完成對總線數據信息的實時校核,如果出現不一致或者非法信息及時切斷驅動單元的供電,在最短時間內使系統導向安全側。

系統方案及硬件實現

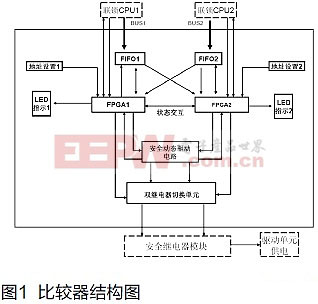

比較器通過兩條總線與兩塊CPU板相連實現總線數據傳輸和比較相關狀態的交互,輸出信號驅動板外安全繼電器模塊實現對驅動單元供電的控制。比較器結構如圖1所示,比較器由如下部分構成:FIFO控制器、FPGA單元、安全動態電路、雙繼電器切換單元、LED指示、地址設置單元。FIFO控制器和FPGA單元由獨立的兩套構成二取二結構,與二取二CPU板相接合。對于二取二比較器的每一部分有獨立的LED指示和總線地址設置單元。安全動態電路和雙繼電器切換單元本身為二取二結構。

數據比較單元

數據比較單元實現兩個CPU板總線數據的同步、獨立安全校核,由雙套FIFO控制器和雙套FPGA單元構成。FIFO控制器用于實現主、從CPU板中總線數據到兩個FPGA的傳輸,其數據存儲空間為8192字節,可完成8k字節以下任意大小的總線數據校核。50萬門級的FPGA通過內部數字時鐘管理模塊(Digital Clock Manager,DCM)將外部時鐘倍頻到40MHz以完成總線數據的高速校核處理。

fpga相關文章:fpga是什么

比較器相關文章:比較器工作原理

評論