遠程無噪傳送高速ADC數據

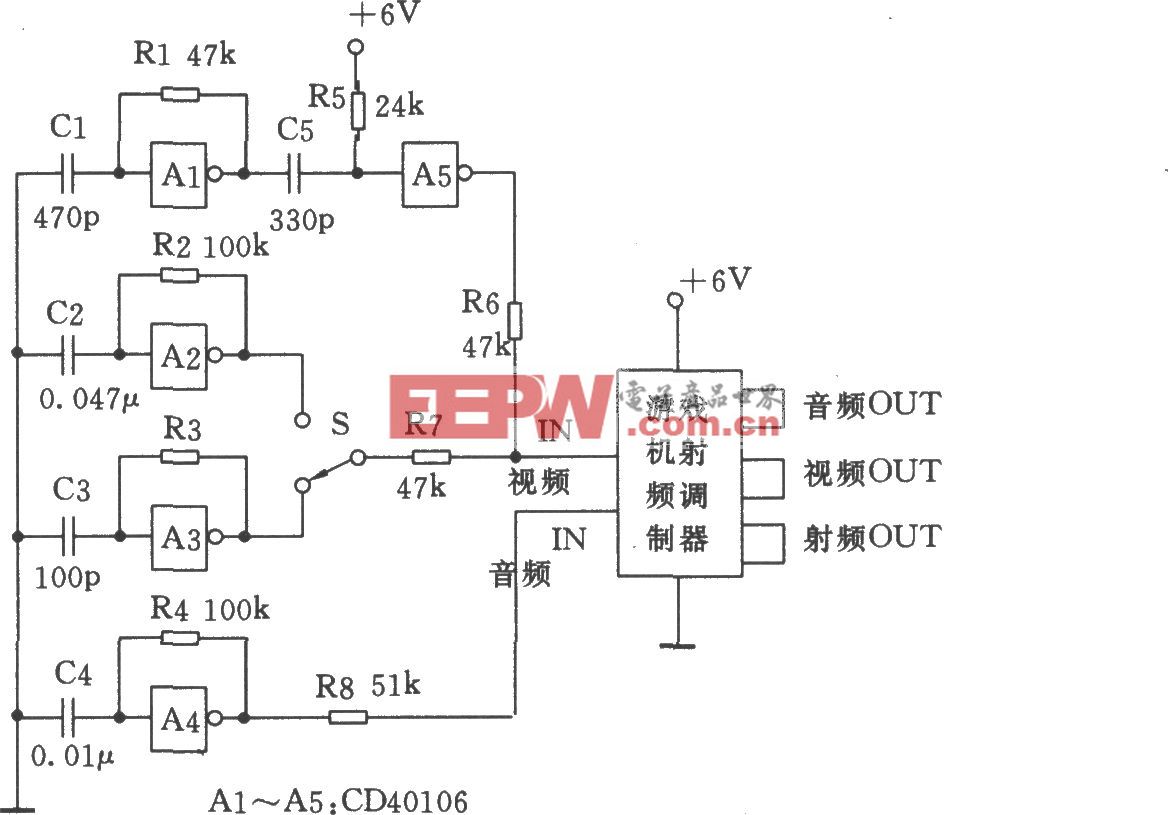

解決問題的一種辦法是采用LVDS(低電壓差分信號)數據總線。圖1示出帶LVDS輸出的ADC框圖,驅動一個ASIC或解串器。此處ADC以LVDC信號格式輸出串行數據流。在接收端,LVDS就緒ASIC或解串器恢復N位輸出。

在上電時序期間,ADC和接收器處理完2步初始化時序。初始化與包含在每個芯片上的PLL同步有關。首先,接收器鎖定到振蕩器頻率。ADC PLL鎖定到CLKIN。在此之后,ADC送出稱之為‘SYNC’圖形的數據時序。這是任意“1”隨后相同“0”數的圖形,定時在輸出數據率。接收器中的PLL鎖定到SYNC圖形,并發送‘LOCK’信號返回到ADC。此信令ADC接收器被鎖定,并為輸入數據準備好。輸出數據由‘起始位’(總是‘1’)、n位數據和‘停止位’(總是‘0’)組成。圖2示出時序流程圖。

因此,FRAME由n+2位組成。數據流頻率為(n+2)x fsample。只要接收器的PLL保持鎖定,接收器就可保持接收數據。若鎖定去除,則LOCK線置為低態,而同步圖形再次請求ADC。

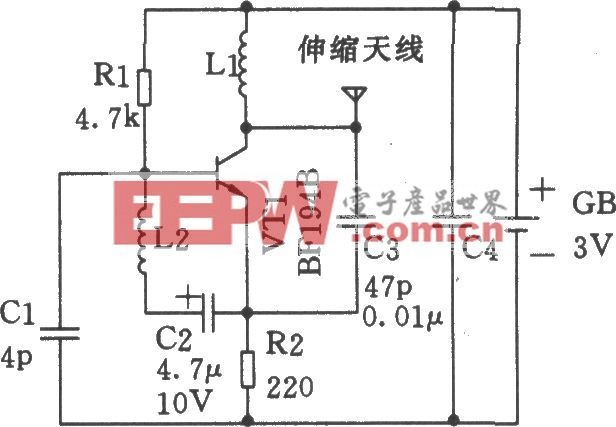

ADC輸出驅動器是電流源,具有驅動100Ω雙絞線、PCB跡線或微帶線的能力。圖3示出靠近接收器的兩個典型終端電路。圖3a示出一個簡單的終端電路,電阻器端接ADC線以降低可能發生的任何反射。它也提供產生輸出信號所需的電流源負載。圖3b也是一個簡單的終端電路,它提供緩沖纜線的共模電阻。除ADC和解串器之間連線數最少外,差分信號格式保持磁場緊緊地包圍在傳輸線周圍。這降低了連線的EMI。■ (冰)

評論