基于Nexys 3開發板的堆棧處理器的測試

前言

本文引用地址:http://www.j9360.com/article/128725.htm堆棧處理器是一種專門面向嵌入式控制領域的處理器,其所有執行過程均依賴于兩個硬件支持的堆棧:執行數學表達式的數據堆棧(Data Stack)和保存子程序返回地址的返回堆棧(Return Stack),而不是大量的通用寄存器。堆棧處理器的特征使其相比較于RISC和CISC等通用寄存器處理器,更加適合應用于嵌入式實時控制領域。本文在上述背景下,介紹了一個堆棧處理器的IP核,給出了其在Digilent公司的Nexys 3開發板上的實現結果,以及使用ModelSim SE 6.5C仿真測試的結果。

堆棧處理器IP核簡介

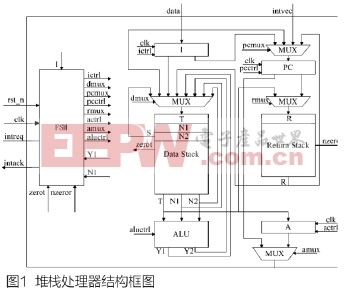

圖1給出了堆棧處理器IP核的結構框圖。從圖中可以看出,本文的堆棧處理器IP核包含兩個堆棧,一個是支持數據運算的數據堆棧,該堆棧由三個棧頂緩沖寄存器T、N1、N2以及一個深度為8的循環緩沖組成;另外一個是支持程序調用的返回堆棧,該堆棧由棧頂寄存器R以及一個深度為8的循環緩沖組成。處理器還包含一個程序計數器PC、一個指令寄存器I和一個地址寄存器A。數據運算則由ALU模塊執行。處理器的所有操作都在有限狀態機FSM控制下完成。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論