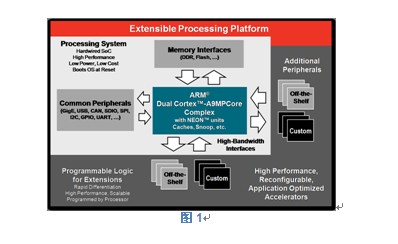

業(yè)界首款基于ARM處理器的可擴(kuò)展式處理平臺(tái)架構(gòu)

對(duì)所有的嵌入式系統(tǒng)來(lái)說(shuō),必然會(huì)在一定的設(shè)計(jì)階段進(jìn)行決策,決定對(duì)給定的應(yīng)用到底是選擇ASSP 還是采用合適的片上系統(tǒng) (SoC) 解決方案。這兩種選擇都需要交替使用并進(jìn)行折衷。如果選用 ASSP,雖然它是一款便于實(shí)施的標(biāo)準(zhǔn)現(xiàn)成解決方案,但對(duì)許多新型應(yīng)用來(lái)說(shuō),會(huì)嚴(yán)重阻礙設(shè)計(jì)團(tuán)隊(duì)的產(chǎn)品定制與差異化能力的發(fā)揮。毫無(wú)疑問(wèn),用 FPGA 或 ASIC 從頭開(kāi)始構(gòu)建 SoC 可以實(shí)現(xiàn)終極定制。盡管一些設(shè)計(jì)團(tuán)隊(duì)能證明構(gòu)建 ASIC 是合理的,但是越來(lái)越多的OEM廠商利用 FPGA,從成本、功耗、密度和性能角度而言提供與ASIC相同的功能,但是風(fēng)險(xiǎn)卻大大降低了。

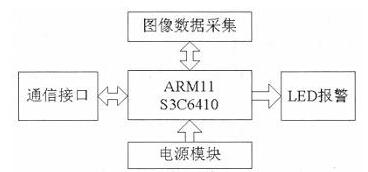

本文引用地址:http://www.j9360.com/article/127575.htm賽靈思可擴(kuò)展式處理平臺(tái)的推出,意味著嵌入式系統(tǒng)設(shè)計(jì)人員在做出決策時(shí)多了一個(gè)新的解決方案選擇,尤其是在把性能、集成度和靈活性視為關(guān)鍵設(shè)計(jì)考慮因素時(shí),該解決方案更是明智之選。以ARM®處理器為核心的解決方案利用 SoC 方法來(lái)降低成本與功耗,增強(qiáng)特性與性能,并將針對(duì)低成本、低功耗優(yōu)化的 28nm FPGA 的優(yōu)勢(shì)與具有嵌入式軟件開(kāi)發(fā)人員熟悉的業(yè)界領(lǐng)先處理器環(huán)境,和生態(tài)系統(tǒng)的完整平臺(tái)相結(jié)合(如圖1 所示)。該新平臺(tái)將整合賽靈思目標(biāo)設(shè)計(jì)平臺(tái)戰(zhàn)略中的許多組件,使軟/硬件設(shè)計(jì)人員能充分利用開(kāi)放式標(biāo)準(zhǔn)、常見(jiàn)設(shè)計(jì)方法、開(kāi)發(fā)工具和運(yùn)行時(shí)間平臺(tái),從而幫助設(shè)計(jì)人員減少開(kāi)發(fā)應(yīng)用基礎(chǔ)設(shè)施所花費(fèi)的時(shí)間,集中精力為最終產(chǎn)品帶來(lái)差異化特性。

系統(tǒng)性能為何重要

盡管許多嵌入式系統(tǒng)只需較低的處理能力實(shí)現(xiàn)系統(tǒng)控制,不過(guò),大量面向視頻監(jiān)控、汽車駕駛輔助、航空與國(guó)防等市場(chǎng)領(lǐng)域的新型應(yīng)用都要求系統(tǒng)必須集成并處理多個(gè)數(shù)據(jù)集,以便做出復(fù)雜的決策,通常是實(shí)時(shí)的決策。我們發(fā)布的新聞稿談到了有關(guān)不同的市場(chǎng)和應(yīng)用。這些新型應(yīng)用的共同之處在于,其所需的系統(tǒng)性能水平大大超出了傳統(tǒng)處理解決方案能夠?qū)崿F(xiàn)的水平。許多這種應(yīng)用基本不能用 ASSP 來(lái)實(shí)現(xiàn),原先簡(jiǎn)單用 ASSP 來(lái)滿足接口、特性和功能要求的情況已經(jīng)不適用了。

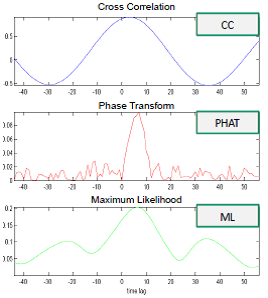

即便性能最高的順序處理器也難以滿足處理多個(gè)進(jìn)入系統(tǒng)的高清數(shù)據(jù)流數(shù)據(jù)輸入的速度要求。舉例來(lái)說(shuō),智能視頻監(jiān)控將多個(gè)分布式視頻捕獲點(diǎn)整合在一起,對(duì)數(shù)據(jù)進(jìn)行預(yù)處理,并傳輸至中央主機(jī)系統(tǒng)或新一代無(wú)線通信系統(tǒng),而這些系統(tǒng)將判定反饋整合起來(lái),實(shí)施高級(jí)自適應(yīng)、預(yù)失真及波束形成算法,這種系統(tǒng)突出反映了應(yīng)用對(duì)出色性能水平的要求。

用硬件提升系統(tǒng)性能

處理器系統(tǒng)主導(dǎo)著嵌入式系統(tǒng)市場(chǎng),同樣發(fā)揮重要作用的還有由軟件開(kāi)發(fā)人員(實(shí)際上軟件開(kāi)發(fā)人員的數(shù)量與硬件工程設(shè)計(jì)人員數(shù)量之比為 10:1)設(shè)計(jì)并實(shí)施成百上千萬(wàn)條高級(jí)代碼。指令集時(shí)延和有限的并行處理能力限制了通用處理器實(shí)施高數(shù)據(jù)強(qiáng)度系統(tǒng)的能力。解決這一難題的常見(jiàn)方法就是采用更多處理引擎同時(shí)處理數(shù)據(jù)。這就要求對(duì)代碼進(jìn)行重新分區(qū),實(shí)現(xiàn)多核實(shí)施,避免重新分區(qū)開(kāi)銷抵消性能增益。

另一種傳統(tǒng)的嵌入式系統(tǒng)方法就是將 FPGA 用作“協(xié)處理器”來(lái)分擔(dān)或加速大量代碼或復(fù)雜算法的處理工作,從而提高處理器和系統(tǒng)效率。設(shè)計(jì)人員通過(guò)在 FPGA 架構(gòu)中執(zhí)行函數(shù),可將函數(shù)性能提升 100 倍,這要?dú)w功于 FPGA相對(duì)于 CPU 的并行處理能力。我們既可采用定制板或模塊上的雙芯片處理器加FPGA解決方案的組合方式,也可采用內(nèi)嵌于FPGA本身的處理器來(lái)實(shí)施。至于多核方法,在 FPGA 中實(shí)施軟件算法不是沒(méi)有缺點(diǎn),考慮到單元成本和實(shí)施復(fù)雜性等因素,更不用說(shuō)涉及到開(kāi)發(fā)需要從傳統(tǒng)通用處理器中調(diào)用軟件算法所需的定制處理引擎和API 等因素。對(duì)這種系統(tǒng)來(lái)說(shuō),性能往往受限于不同技術(shù)之間的 I/O 接口,特別是涉及到雙芯片時(shí)更是如此。

許多 DSP 系統(tǒng)都利用采用特定處理參數(shù)的專用高性能處理引擎。這種分區(qū)方法比較簡(jiǎn)單,而且比傳統(tǒng)的通用順序處理引擎性能更高,但軟件可調(diào)用的處理單元數(shù)量有限,因此會(huì)限制處理能力。

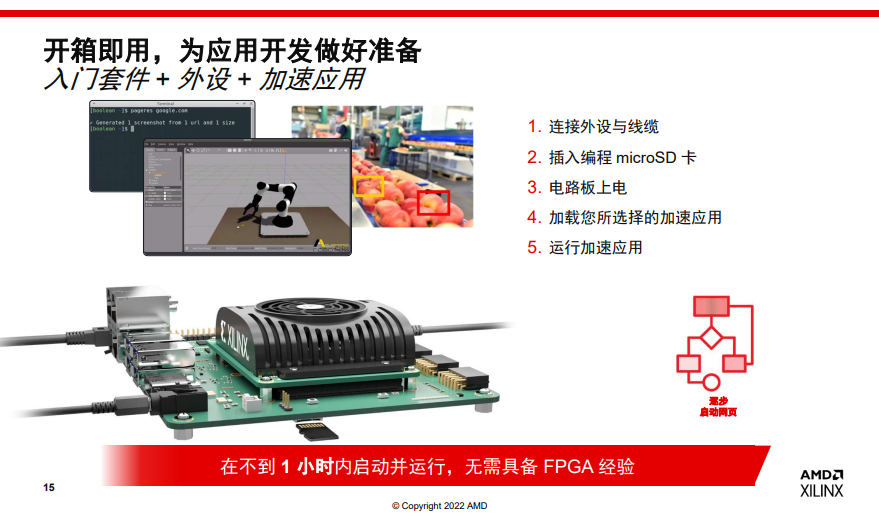

賽靈思可擴(kuò)展式處理平臺(tái)將雙核 ARM Cortex™-A9 MPCore™ 處理器與關(guān)鍵外設(shè)及可編程邏輯完美整合在一起,解決了其他擴(kuò)展系統(tǒng)性能的解決方案的許多技術(shù)局限性問(wèn)題。處理器和 28 nm芯片可編程邏輯之間的 AMBA® 互聯(lián)機(jī)制確保不會(huì)出現(xiàn)降低系統(tǒng)性能的I/O瓶頸。這種新型架構(gòu)為設(shè)計(jì)團(tuán)隊(duì)帶來(lái)增值,使其能在 Cortex-A9 處理器和可編程邏輯擴(kuò)展模塊之間進(jìn)行功能平衡取舍。

過(guò)去十年來(lái),整合 SoC 和 FPGA 兩大領(lǐng)域并包括可編程邏輯處理器的處理平臺(tái)穩(wěn)步發(fā)展,這要?dú)w功于采用 FPGA 邏輯資源的軟處理器內(nèi)核的發(fā)展,以及嵌入 FPGA 內(nèi)部作為專用資源的硬連線微處理器內(nèi)核的出現(xiàn)。類似于賽靈思自己的 MicroBlaze® 處理器的軟核處理器在可配置性和低成本方面優(yōu)勢(shì)明顯,但只有先圍繞其構(gòu)建子系統(tǒng)后才能開(kāi)始開(kāi)發(fā)。目前很多 FPGA 中構(gòu)建的處理器都沒(méi)有堅(jiān)實(shí)的子系統(tǒng),雖然比軟核處理器提升了性能,但需要大量配置,然后才能讓該處理器系統(tǒng)啟動(dòng)并運(yùn)行起來(lái)。簡(jiǎn)而言之,上述這兩種模式都是以硬件為核心的方法,目前全球很多 FPGA 開(kāi)發(fā)人員都在成功實(shí)踐。

評(píng)論