為您的轉換器選擇正確的時鐘(4)

預計結果

本文引用地址:http://www.j9360.com/article/123865.htm正確設計適當的時鐘電路是比較困難的任務。但只要牢記本文涵蓋的各個方面,對實現成功的設計大有幫助。總之,寬帶噪聲必須適合所需的信噪比性能,時鐘雜散必須適合所需的雜散輸出水平。許多SW(軟件)工具有助于成功的設計,包括ADIsimPLL[3]和ADIsimCLK[4]。這些工具可從參考文獻段落中提供的鏈接免費下載。

圖21“典型時鐘電路”顯示的是典型的時鐘凈化、合成和分配網絡。該網絡旨在拾取不太干凈的輸入時鐘,例如網絡時鐘,消除大部分時鐘抖動并產生穩(wěn)定的基準源,后者則可用于在此基礎上合成任何所需的數據轉換器時鐘。圖中未詳細顯示可用于合成本振和其他導出時鐘的額外PLL網絡,但其設計方式類似。

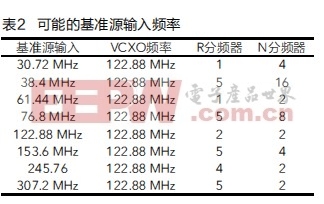

在典型應用中,時鐘和合成器必須與外部來源同步。許多情況下,必須接受特定頻率范圍,例如表2“可能的基準輸入頻率”所示。此外,這些外部基準源一般會帶來相對大量的噪聲。為此,需要較窄的環(huán)路濾波器。由于該合成器的輸出是固定頻率,且需要較高性能,應優(yōu)先選擇VCXO而不是VCO,以確保高性能和極低的輸出相位噪聲。在此示例中,選擇了Taitien的122.88 MHz VCXO。該應用選擇了ADF4002 PLL。由于是固定頻率應用,鎖定時間不是首要因素,因此窄環(huán)路濾波器有助于盡可能減少基準源噪聲。對于此應用,選擇了1 kHz環(huán)路濾波器,如圖22“時鐘凈化PLL”所示。

評論