系統級可編程能力助力嵌入式應用

在您曾經從事的嵌入項目中,有多少在項目生命周期各階段成功過渡而不需要重做系統設計、物料清單、布線等呢?如果您的答案與嵌入業界的大部分人一樣低于百分之百,則您可以考慮采用嵌入設計的一種新方法,它有望節省您的時間、金錢和煩惱。本文中,我們將探討您日常面對的嵌入設計挑戰,并以實用的方式探討如何運用系統級的可編程能力克服這些挑戰。首先,簡介什么是真正的可編程能力。

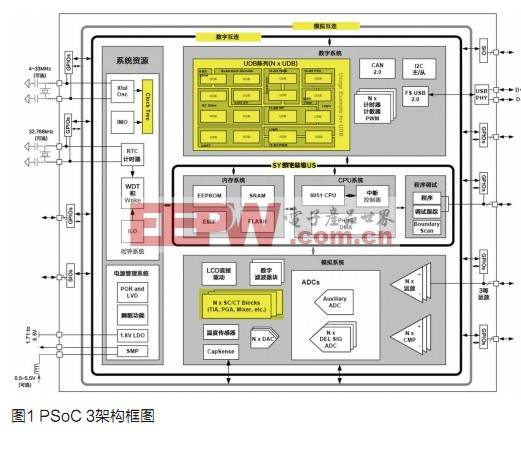

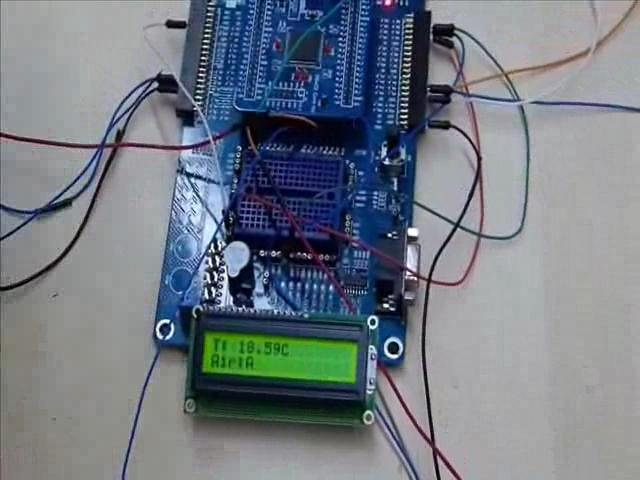

本文引用地址:http://www.j9360.com/article/101087.htm我們將這一話題分為三部分分別進行說明:編程能力、系統級、真正。可編程能力不應與可配置能力混淆,而是指使用基本結構塊構建功能的能力。該定義下,這些基本結構塊在硬件中實施,并通過配置寄存器、數據路徑和信號路徑共同用于構建某個功能。例如,圖1中描述了賽普拉斯(Cypress)下一代PSoC設備架構PSoC 3 和 PSoC 5中實施真正系統級可編程能力的基本結構塊。圖中突出顯示的這些基本結構塊包括高性能的8位8051 (PSoC 3) 或32位ARM Cortex M-3 (PSoC 5) 處理器、可編程時鐘樹、Universal Digital Block (UDB,通用數字塊)、可編程模擬塊和可編程路由和相互連接(模擬、數字和系統總線)。

PSoC 3和 PSoC 5架構中的時鐘系統使一組模擬和數字時鐘支持各種外圍設備,例如ADC、PWM、計數器等。八個單獨源的 16 位時鐘分頻器用于數字系統外設,四個單獨源的 16 位時鐘分頻器用于模擬系統外圍設備,所有分頻器與一套四個內部或二個外部時鐘脈沖源連接,形成強大的時鐘數。

每個 UDB 是一個非常強大、靈活的數字邏輯時鐘。PSoC 3 和 PSoC 5 架構中的每個 UDB 包括一個基于 ALU 的八位數據路徑、兩個細粒度 PLD、一個控制和狀態模塊以及一個時鐘和復位模塊。這些元件可以共同執行低端微控制器的功能,也可以將它們與其他UDB連接起來實現更大的功能,或者由他們實現數字外圍設備,例如定時器、計數器、PWM、UART、I2C、SPI、CRC等,某些PSoC 3和 PSoC 5設備家族采用24個UDB,您甚至可以在8051或ARM Cortex-M3 處理器的基礎上實現 24 核處理器,或內部 DMA(一個非常強大的架構)。

評論