高速PCB電路板信號完整性測試的方法有哪些?

信號完整性測試是高速PCB設計中的關鍵環節,直接影響產品的可靠性和性能。

高速PCB在現代電子設備中廣泛應用,如服務器、通信設備和消費電子,信號速率的提升使得反射、串擾等問題的檢測變得尤為重要。

研究表明,適當的測試方法可以顯著降低設計迭代成本,提高產品上市速度。

信號完整性問題源于高速信號傳輸中的物理特性,主要包括以下幾個方面:

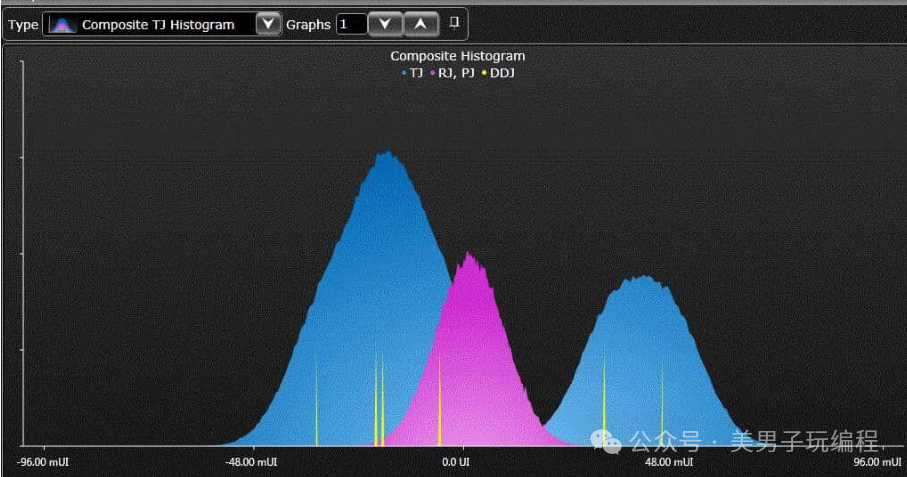

反射:當傳輸路徑中存在阻抗不匹配時,信號部分反射回源,類似于聲波遇到障礙物反彈。研究表明,這可能導致信號失真和時序錯誤,特別是在高頻信號下更為顯著。串擾:相鄰信號跡之間的電磁耦合引起干擾,類似于無線電信號的交叉干擾。證據傾向于密集布線設計更容易引發串擾,尤其在高密度PCB中。時序問題:時鐘和數據信號的同步性至關重要,任何偏差可能導致數字電路的建立和保持時間違規,影響數據完整性。抖動與噪聲:抖動表現為信號轉換時間的隨機變異,噪聲則是任何非預期電信號,可能改變信號的幅度或相位。兩者共同影響信號的可靠傳輸。

電源完整性問題:電源供應的波動或噪聲可能通過電源平面傳播,間接影響數字組件的運行,導致信號完整性下降。

信號完整性測試的目標是量化這些問題,優化信號波形質量,并及早識別潛在問題以改進設計。

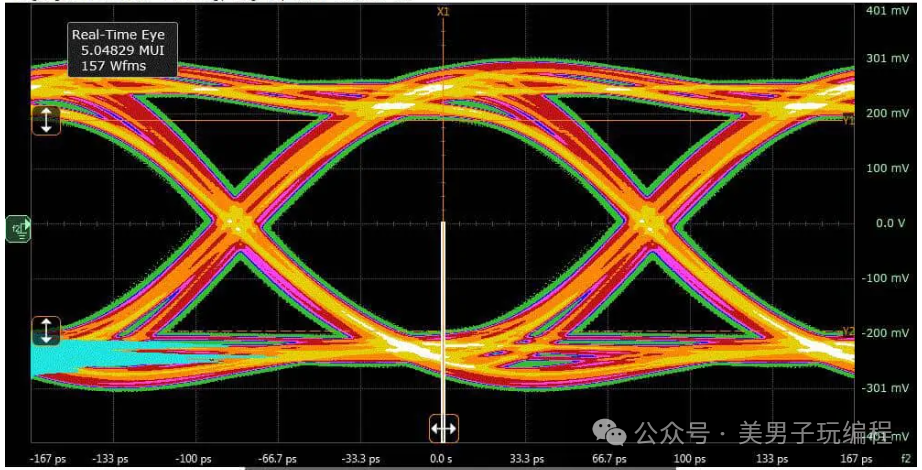

例如,通過分析眼圖的開眼度,可以直觀判斷信號的時序裕量和噪聲水平。

常用測試方法的分類與分析

測試方法可分為時域、頻域和模擬實驗三大類,每類方法針對不同信號完整性問題提供獨特的洞察。

時域測試的詳細說明

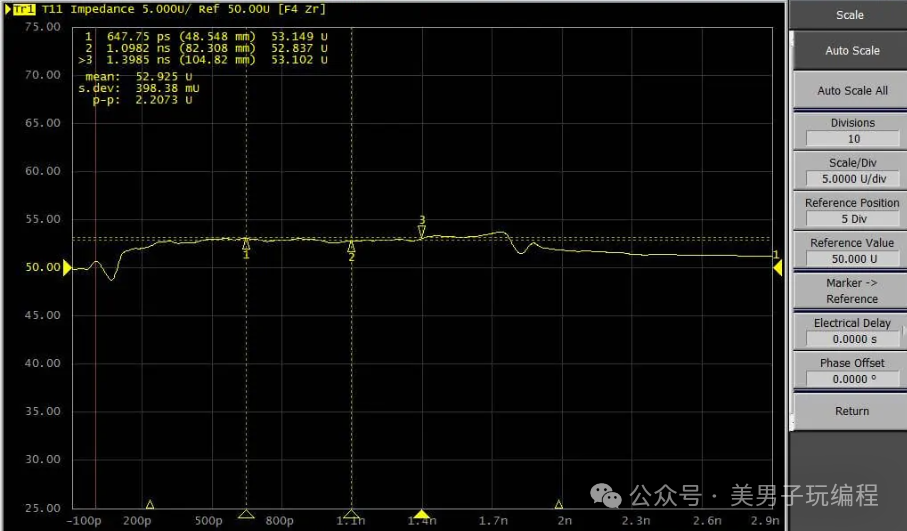

時域反射測量(TDR):TDR通過發送階躍或脈沖信號并觀察反射波形,評估傳輸線的阻抗特性。研究表明,TDR特別適合檢測阻抗不匹配位置,如連接器或過孔處的突變。應用場景包括確定傳輸線長度和評估組件質量,工具如TDR測試儀或高端示波器,優勢在于快速定位問題區域,直觀反映阻抗分布。

眼圖分析:眼圖通過疊加多個數字信號周期,分析抖動、噪聲和碼間干擾(ISI)。眼圖的開眼寬度表示時序裕量,開眼高度表示幅度裕量,閉合的眼圖通常提示過多抖動或噪聲。適用于測試PCIe、SATA、DDR等高速接口,工具為高速實時示波器,適合評估數據傳輸的穩定性和裕量。

頻域測試的深入探討

S參數測試:使用矢量網絡分析儀(VNA)測量散射參數(S參數),量化頻域傳輸特性。S11表示回波損耗,S21表示插入損耗,研究表明這些參數對評估傳輸線、連接器和過孔的高頻性能至關重要。應用場景包括測量信號帶寬和頻率響應,工具為VNA,適合寬頻段分析,特別是高速信號的高頻部分。EMI/EMC測試:使用頻譜分析儀測量PCB發射的電磁波,評估電磁干擾水平。雖然EMI/EMC測試主要關注電磁兼容性,但研究顯示,信號完整性問題可能導致EMI增加,反之亦然。應用場景包括確保設計符合EMC標準,檢測串擾和輻射噪聲,工具包括頻譜分析儀和近場探頭。

模擬與實驗結合的實踐

模擬測試:使用電磁模擬工具如HFSS(高頻結構模擬器)、ADS(高級設計系統)和HyperLynx,在設計階段預測信號完整性問題。模擬可以建模傳輸線、過孔和連接器的特性,研究表明,這在無物理板時驗證設計合理性非常有效,但依賴設計參數的準確性。實驗驗證:PCB制作完成后,通過TDR、眼圖、S參數等方法驗證模擬結果的正確性。實驗驗證是確保模擬模型準確性的關鍵步驟,研究建議結合多種方法綜合評估,以發現模擬可能忽略的實際問題。

測試工具與設備的選擇

以下是常用工具的詳細列表及其用途,研究表明,選擇合適工具需考慮測試需求和設備精度:

實施建議的最佳實踐

實施信號完整性測試需遵循以下步驟:

預測試準備:確保PCB清潔、無污染,接地良好,選擇合適的探頭和設備。研究表明,接地不良可能引入額外噪聲,影響測試結果。綜合測試方法:結合時域(如TDR)和頻域(如S參數)方法,全面評估信號行為。例如,同時使用TDR和S參數測試可評估傳輸線性能。測試結果分析:深入分析波形,結合理論知識判斷根因。如眼圖閉合通常提示過多抖動或噪聲,需進一步優化設計。驗證與改進:基于測試數據調整設計,如優化阻抗控制、調整布線或改進電源平面布局,進行迭代優化。研究顯示,迭代設計可顯著提升信號完整性。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。