Vivado Design Suite 用戶指南:動態功能交換

FPGA 技術支持靈活開展現場編程和再編程,無需通過設計修改來重建互連結構。Dynamic Function eXchange (動態功能交換,DFX)推動這一靈活性進一步發展,允許通過加載動態配置文件(通常是部分 BIT 文件)來修改工作中的 FPGA 設計。在使用完整 BIT 文件配置 FPGA 后,可下載部分 BIT 文件以修改 FPGA 中的可重配置區域,在未經重配置的器件各部分中運行的應用的完整性則不會受到任何影響。

DFX 是由多個部分組成的綜合性解決方案。這些要素包括:AMD 芯片能進行動態重配置,Vivado? 軟件流程支持編譯設計(從 RTL 到比特流),以及各種補充性功能特性(如 IP)。在此版本中,您將看到 DFX 與部分重配置( PR )術語混用,其中 DFX 表示整體解決方案,PR 則表示該解決方案的技術組成部分。

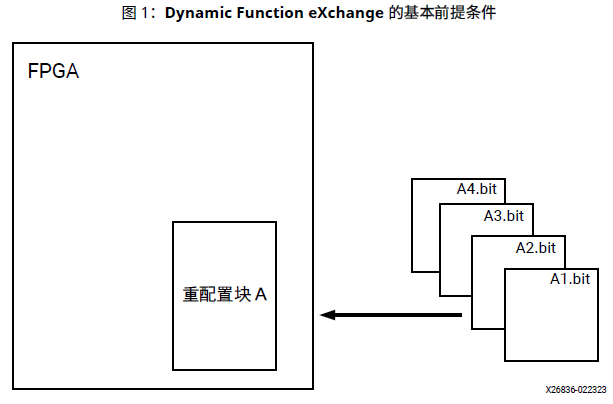

下圖顯示了 Dynamic Function eXchange 背后的前提條件。

如圖所示,通過下載下列任一部分 BIT 文件即可修改重配置塊 A 中實現的函數:A1.bit、A2.bit、A3.bit 或A4.bit。FPGA 設計中的邏輯分為 2 種不同類型:可重配置邏輯和靜態邏輯。FPGA 塊的灰色區域表示靜態邏輯,塊中標記為重配置塊 A 的部分則表示可重配置邏輯。靜態邏輯保持正常工作,不受加載部分 BIT 文件的影響。可重配置邏輯則替換為部分 BIT 文件的內容。

在單一 FPGA 上對多路復用硬件進行動態定時的能力是很有用的,原因有很多。其中包括:

▅ 減小實現給定函數所需 FPGA 的大小,從而降低成本和功耗

▅ 支持靈活選擇可用于某一應用的算法或協議

▅ 啟用設計安全性方面的新技術

▅ 改善 FPGA 容錯能力

▅ 加速可配置計算

▅ 向已部署的系統交付更新(修訂和新增功能特性)

除了減小大小、降低權重、功耗和成本外,Dynamic Function eXchange 還能支持無法以其它方式實現的多種新型 FPGA 設計。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。