設計一顆2nm芯片,至少要7.25億美元!

來源:半導體行業觀察(ID:icbank)

近日,Marvell高管在一場分析會上表示,隨著制程工藝的演進,芯片的研發成本正在飆升。

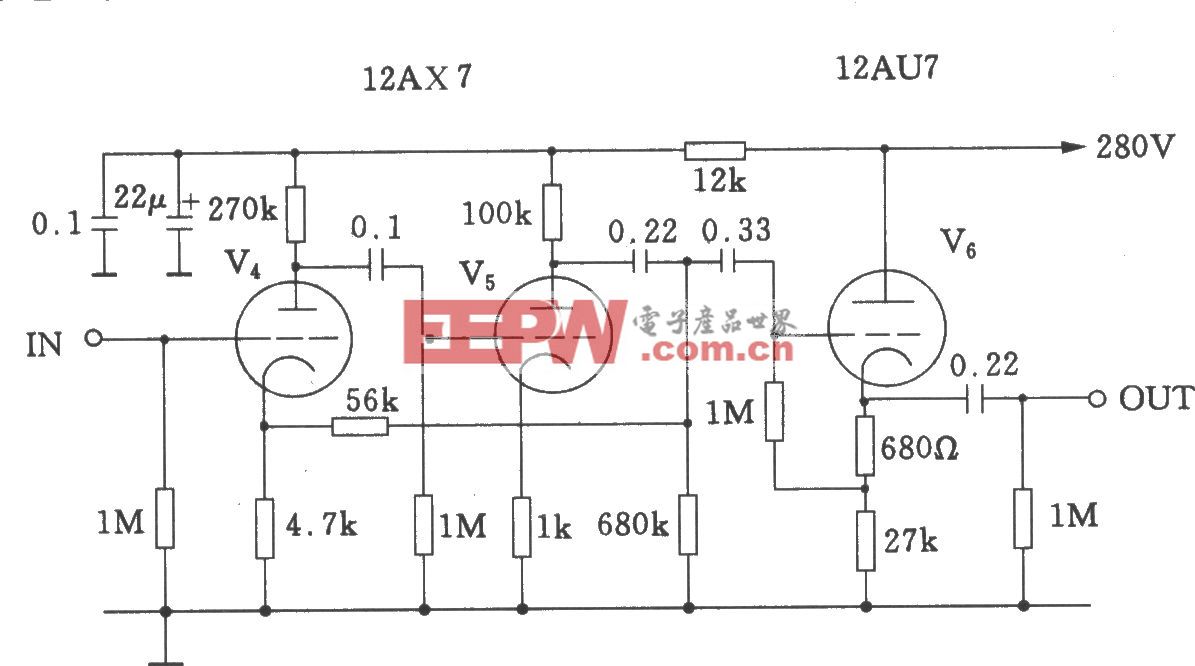

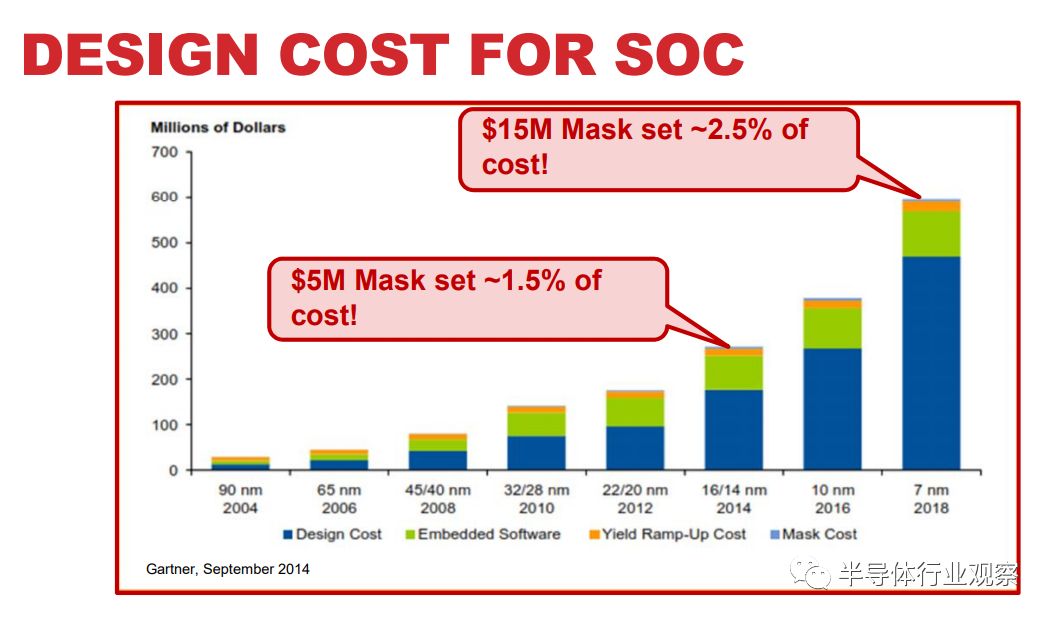

如下圖所示,在28nm的時候,設計一顆芯片的成本僅為4280萬美元。在接下來的的22和16nm,芯片設計成本有穩步上升,但幅度還是可控。到了10nm一下,芯片成本則同步飆升。

芯片工藝越來越先進了,今年三星量產了3nm工藝,臺積電的3nm也是箭在弦上了,明年就會是3nm的高光時代,2024到2025年則是2nm工藝量產。

先進工藝生產出來的芯片性能更強大,能效也更好,但這也不是沒有代價的,最大的麻煩就是燒錢,不僅是3nm、2nm工廠建設需要200億美元以上的資金,哪怕是AMD、NVIDIA、蘋果、高通這樣的芯片設計公司,開發一款芯片的成本也會越來越高。

在前不久的IEDM會議上,Marvell公司公布了一些數據,援引IBS機構分析了各個工藝下芯片開發成本,其中28nm工藝只要4280萬美元,22nm工藝需要6300萬美元,16nm工藝需要8960萬美元。

后面的先進工藝開發成本就直線上漲,7nm需要2.486億美元,5nm需要4.487億美元,3nm需要5.811億美元,而2nm工藝需要的開發資金是7.248億美元,人民幣約合50億。

換句話說,如果某家公司想要自己搞一款先進工藝芯片,比如2nm處理器,不說設計周期要幾年時間,光是投入的資金就得50億元。

還不算生產的費用,2nm代工價格現在還沒有,但是3nm工藝就要2萬美元以上了,漲價25%。

照這樣發展下去,未來2nm的CPU及顯卡就算能做出來,成本也會一路上漲,在這個方向上已經沒有退路了。

在筆者看來,按照這個增長幅度,芯片設計成本突破10億美元指日可待。

從Marvell分享的這個圖我們可以看到,在芯片設計成本中,軟件占了大頭,緊隨其后的是Verification、Validation、physicical、IP qualification、prototype和architecture。按照上頭的展示,本來在28nm的時候,軟件就是芯片設計的最巨大的成本,但這種情況在22nm和16nm的時候被扭轉了。但進入到了10nm以后,這種情況重新出現。由此可以看到先進工藝給芯片設計產業帶來的挑戰。

先進制程芯片成本為啥這么貴?

- 晶圓代工成本

根據CEST的模型,在5nm節點上構建的單個300mm晶圓的成本約為16988美元,在7nm節點上構建的類似晶圓成本為9346美元。可以看到,相同尺寸晶圓,5nm工藝節點相比7nm每片晶圓代工售價高7000多美元。

按節點計算2020年每個芯片的代工銷售價格(圖源:CSET)

按節點計算2020年每個芯片的代工銷售價格(圖源:CSET)從中可以推斷出,在3nm節點上構建的晶圓成本或將達到3萬美元左右,晶圓代工成本將進一步提高。

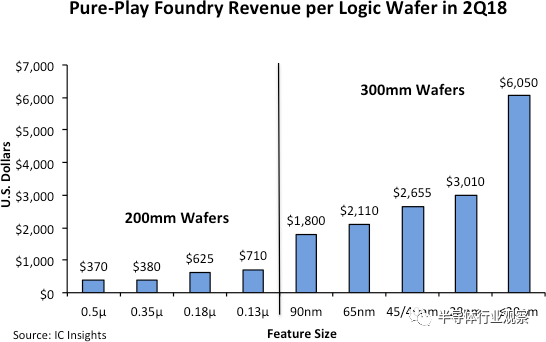

另一組數據也對此進行了印證,成本價格在很大程度上取決于芯片制程和晶圓尺寸的不同。IC Insights提供的數據顯示,每片0.5μ 200mm晶圓代工收入(370美元)與≤20nm 300mm晶圓的代工收入(6050美元)之間相差超過16倍。即使同樣是在300mm晶圓尺寸下,≤20nm 相比28nm工藝,成本相差也達到一倍。

2018年主要技術節點和晶圓尺寸的每片晶圓代工收入(圖源:IC Insights)

2018年主要技術節點和晶圓尺寸的每片晶圓代工收入(圖源:IC Insights)可見,隨著工藝節點的提升,晶圓代工成本隨之大幅度提升。

- 掩膜(Mask)成本

據IBS數據顯示,在16/14nm制程中,所用掩膜成本在500萬美元左右,到7nm制程時,掩膜成本迅速升至1500萬美元。

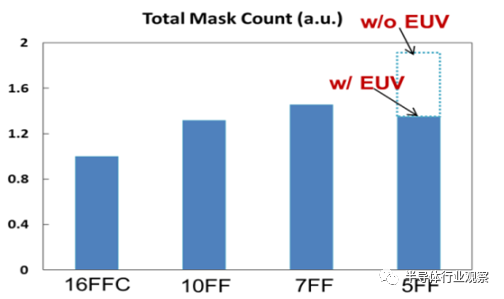

又從臺積電(IEDM 2019)了解到,從10nm到5nm,隨著EUV光刻技術的應用,掩膜使用數量有所減少,5nm與10nm制程中掩膜使用數量相差不多。

不同制程中的Mask數量(圖源:臺積電)

不同制程中的Mask數量(圖源:臺積電)但是,在掩膜數量基本持平的情況下,更先進的制程工藝使得掩膜總成本提升,能側面反映出掩膜平均成本在不斷升高。

再反映到芯片成本上,每片CPU的掩膜成本等于掩膜總成本/總產量。如果總體產量小,芯片的成本會因為掩膜成本而較高;如果產量足夠大,比如每年出貨以億計,掩膜成本被巨大的產量分攤,可以使每塊CPU的掩膜成本大幅降低,使擁有“更貴的制程工藝+更大的產量”屬性的CPU,比“便宜的制程工藝+較小的產量”的CPU成本更低。

可以預見,到3nm時,掩膜成本預計將會再度攀升,進一步增加芯片成本。

- EUV光刻機

隨著工藝制程的發展,到7nm及更先進的技術節點時,需要波長更短的極紫外(EUV)光刻技術來實現更小的制程。荷蘭ASML是全球唯一有能力制造EUV光刻機的廠商。

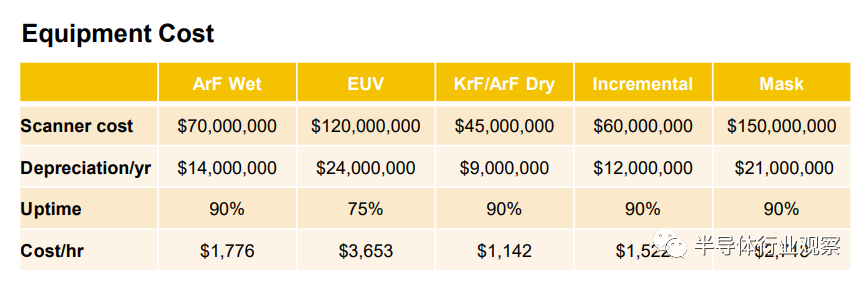

但EUV光刻機的價格一直以來十分昂貴,2018年,中芯國際和ASML簽訂了訂購協議,以1.2億美元的價格訂購了一臺EUV光刻機。這一價格與PHOTRONICS披露的EUV光刻機價格基本吻合。

設備成本(圖源:PHOTRONICS)

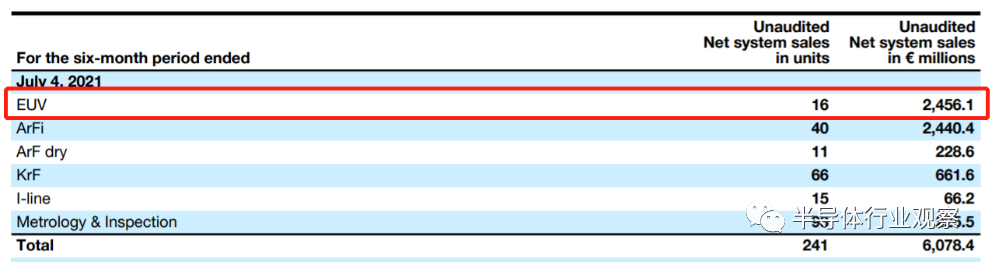

設備成本(圖源:PHOTRONICS)從ASML最新公布的2021年第二季度財報來看,截止2021年7月4日,ASML今年出貨EUV光刻機16臺,銷售額達到24.561億歐元,平均每臺EUV光刻機價格高達1.535億歐元。

ASML 2021年Q2財報(圖源:ASML)

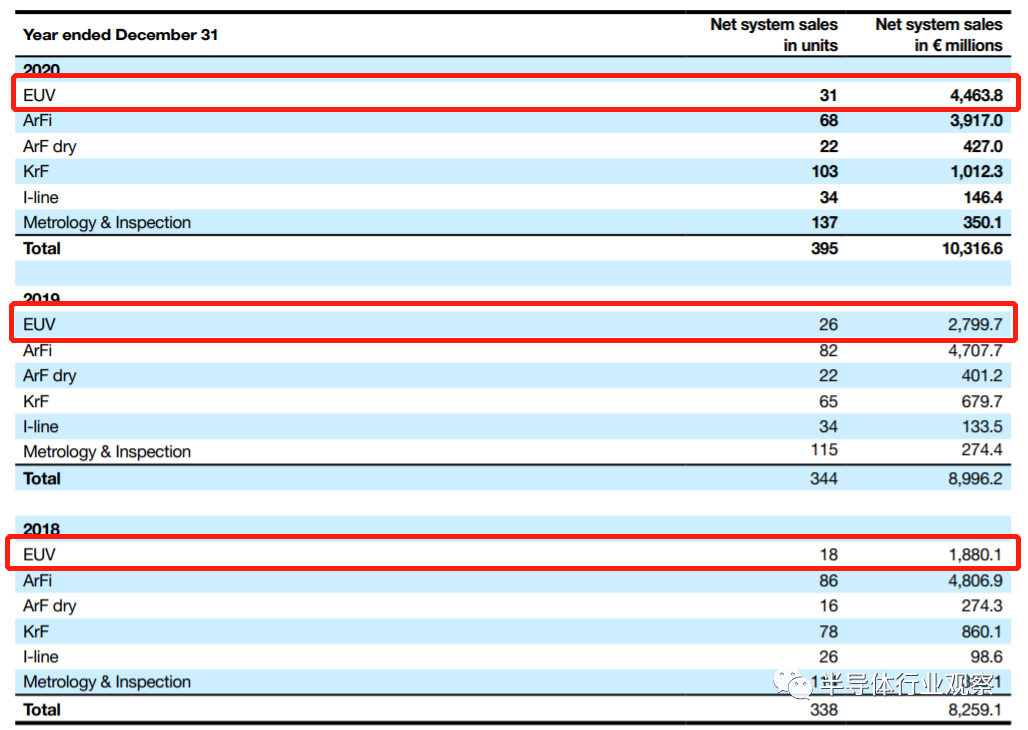

ASML 2021年Q2財報(圖源:ASML)再結合ASML歷年(2018/2019/2020三年)財報數據,能夠看到ASML的EUV光刻機單從1.045億歐元到1.44億歐元,價格逐年攀升。

ASML 近三年財報(圖源:ASML)

ASML 近三年財報(圖源:ASML)一臺EUV光刻機售價超過1億美元,而且還相當不好買。ASML每推出一代EUV光刻機,新設備的生產能力在穩步提升,但價格自然更高。據披露,ASML第二代EUV光刻機將會是NXE:5000系列,進一步提高光刻精度,原計劃2023年問世,現推遲到2025-2026年,而價格預計將突破3億美元。

當然,除了價格最貴的EUV光刻機之外,沉積、刻蝕、清洗、封裝等環節所采用的設備和材料也價格不菲,且成本都在隨著工藝制程向前發展不斷提高。

- 研發&人力成本

先進制程不僅需要巨額的建設成本,高昂的研發和人力費用也提高了設計企業的門檻。

人力成本是研發成本的重要部分,項目開發效率和質量與工程師數量和水平相關,國內資深芯片設計工程師年薪一般在50-100萬元之間。

另一方面,晶體管架構轉向GAA,也在增加芯片成本。

當前隨著深寬比不斷拉高,FinFET逼近物理極限,為了制造出密度更高的芯片,環繞式柵極晶體管(GAAFET)成為新的技術選擇。因此,晶體管結構從FinFET走向GAA,成為摩爾定律續命的關鍵。

- EDA成本

根據ESD Alliance數據顯示,2020年EDA全球市場規模114.67億美元,相對于幾千億美元的芯片市場來說占比較小,但EDA對芯片設計的效率和成本都起著至關重要的作用。

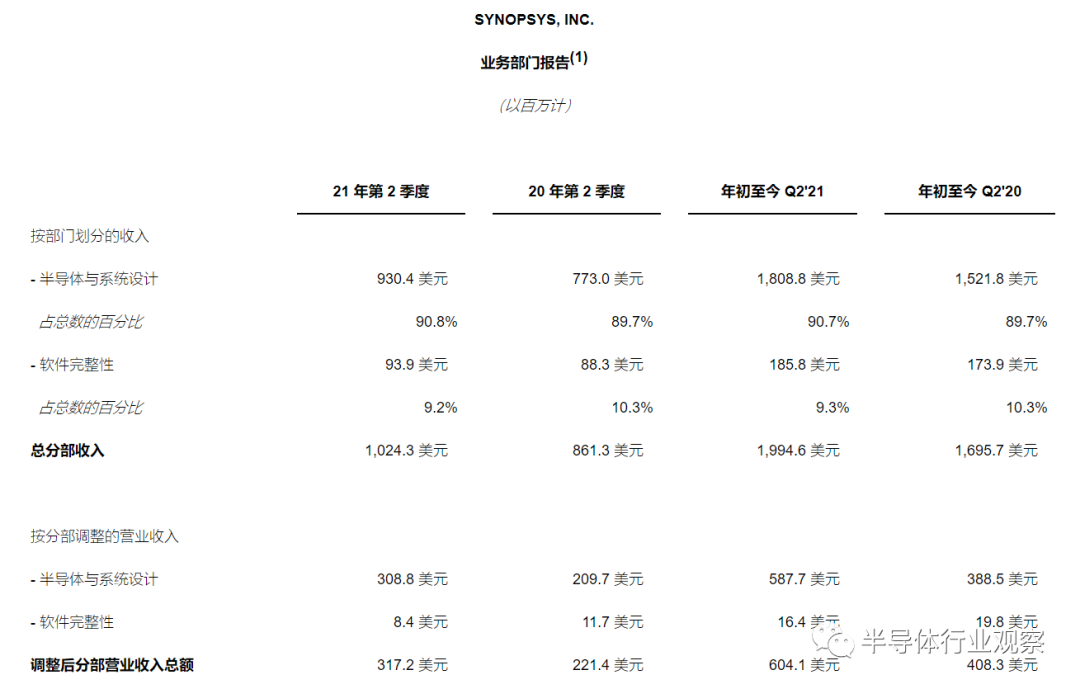

Synopsys 2021年Q2財報(圖源:Synopsys)

Synopsys 2021年Q2財報(圖源:Synopsys)根據Synopsys 最新財報來數據,2021年第二季度營收10.243億美元,半導體和系統設計,包括EDA工具、IP產品、系統集成解決方案和相關服務;軟件完整性,包括用于軟件開發的安全和質量解決方案等。EDA營收達到5.876億美元,占比在57%左右。

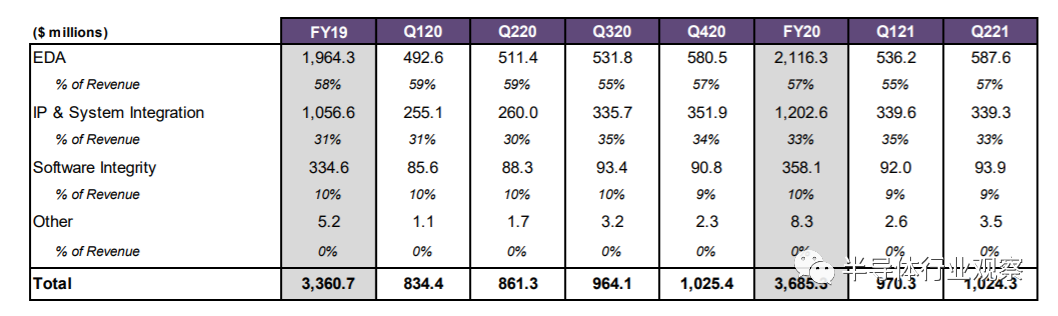

Synopsys財報數據(圖源:Synopsys)

Synopsys財報數據(圖源:Synopsys)據網上數據,20人的研發團隊設計一款芯片所需要的EDA工具采購費用在100萬美元/年(包括EDA和LPDDR等IP購買成本)。從EDA的行業屬性及高昂的研發投入能夠預測,待到3nm制程時,EDA工具授權費自然更是不菲。

- IP授權成本

半導體IP是指在集成電路設計中那些已驗證、可復用、具有某種確定功能和自主知識產權功能的設計模塊,芯片公司可以通過購買IP實現某個特定功能(例如ARM的Cortex系列CPU、Mali系列GPU IP授權等,其他小的模塊也要購買,如音視頻編****、DSP、NPU...等),這種類似“搭積木”的開發模式可大大縮短芯片的開發周期,在降低芯片設計難度的同時提高性能和可靠性。

2017-2020年Synopsys營收拆分(單位:百萬美元)

2017-2020年Synopsys營收拆分(單位:百萬美元)可見,IP作為技術含量最高的價值節點,隨著芯片制程越來越先進,芯片價格的提升,IP研發難度和授權費用也將隨之升高。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。