利用IBERT IP核實現GTX收發器硬件誤碼率測試實例

1. 引言

Vivado中提供了1種IBERT工具用于對Xilinx FPGA芯片的高速串行收發器進行板級硬件測試。通過IBERT我們可以獲取誤碼率,觀察眼圖,調節串行收發器的參數,從而有助于判斷可能存在的問題,便于驗證硬件的穩定性和信號完整性。本測試實例教程使用IBERT工具對與SFP連接的GTX進行5 Gbps速率下的測試。從誤碼率和眼圖兩個角度來驗證電路板GTX部分工作的穩定性和可靠性。本測試實例基于Vivado 2019.1版本開發。

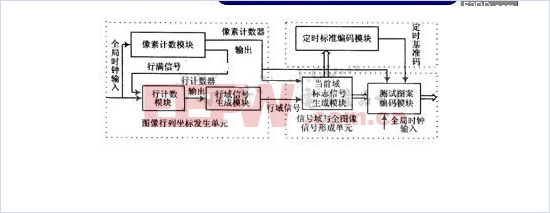

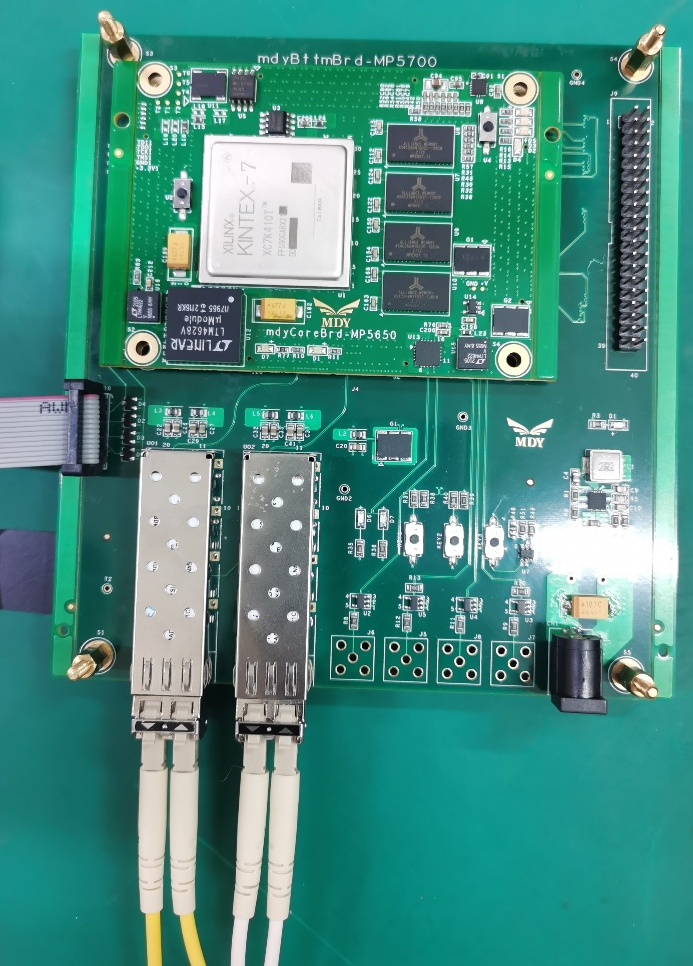

本測試實例是在購買的明德揚(MDY) K7核心板上進行的,這款核心板能夠方便二次開發利用。在FPGA 芯片的HP 端口上掛載了4片DDR3存儲芯片,每片DDR3 容量512 MB 字節,組成64bit 位的數據位寬。4個板對板連接器擴展出了276個IO,全部IO的電平可以通過更換核心板上的磁珠來修改,滿足用戶對+3.3V、+2.5V、+1.5V電平接口的需求,另外也擴展出了16對高速收發器GTX接口。供電范圍大,5-12V電壓均可。通過手冊了解到同一個BANK管腳到連接器接口之間走線做了等長和差分處理。該核心板的結構示意圖如圖1。

圖1 該核心板結構示意圖

2. 測試原理

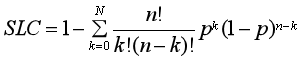

IBERT中的BERT是Bit Error Ratio Test的縮寫,指比特出錯概率測試,簡而言之就是誤碼率測試。誤碼率(Bit Error Rate,BER)作為高速數據傳輸技術中的重要指標,它代表了數據傳輸的可靠性。對于數字通信系統,BER可以定義為出現錯誤碼的估計概率。這意味著任何通過系統傳輸的比特都可能被錯誤地接收。因此,發送的“1”接收到為“0”,或傳輸為“0”被接收到的為“1”。在實際測試中,誤碼率是通過系統傳輸一定比特的比特數和計算接收到的不正確的比特數來測量的。誤碼率是接收到的錯誤比特數與傳輸的總比特數之比。利用累積分布函數定義置信系數SLC(Statistical Level of Confidence):

式中,N為傳輸中發生錯誤的比特數,n為傳輸的總的比特數,p = 10-12,通過置信系數得到在傳輸n bit后誤碼率為:

式中,BER 傳輸n bit發生錯誤概率,ln[.]是自然對數。當沒有檢測到錯誤(N = 0)時,式5.7中的第二項等于零,方程的求解得到了很大的簡化。

首先對明德揚Xilinx K7核心板光纖接口進行了誤碼率。Vivado中IBERT工具的測試原理是通過收發器由外部回環進行自收自發而實現。就是將同一組收發器的TX和RX進行短接,TX發送端通過發送某種特定序列的數據流,在RX接收端接收后,通過比對發送和接收的數據,從而得出接收端誤碼的統計值。將光模塊插入SFP屏蔽籠內,然后通過單根光纖將光模塊的TX和RX短接,便可以通過IBERT工具對GTX進行測試。

3. QUAD(GTX BANK)、CHANNEL、GTX間的關系

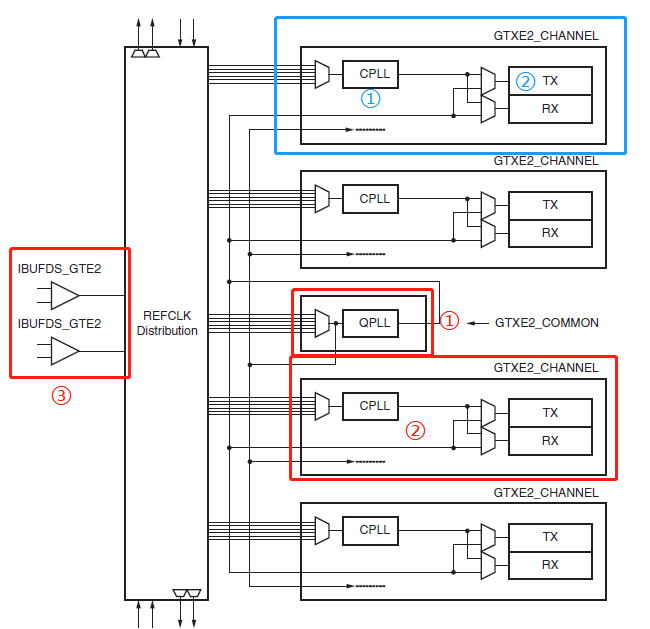

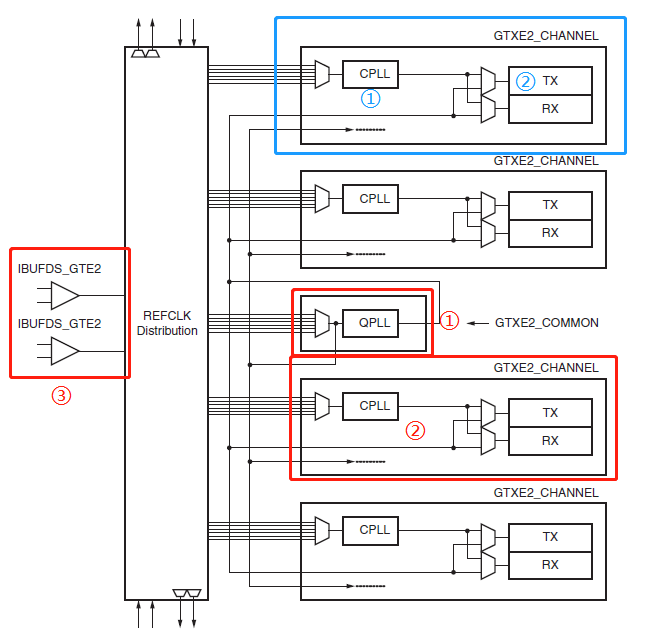

首先可以從圖2中看到XC7K325T中共有16個GTX,每4個GTX組成一個Bank,稱為Quad,即XC7K325T芯片共有4個Quad。

圖2 Kintex-7 FPGA(XC7K325T)GTX結構圖

如圖3所示,具體看Quad布局圖,可以看到一個Quad包含4個GTX_channel(簡稱GTX或channel)和一個QPLL。

圖3 Quad布局圖

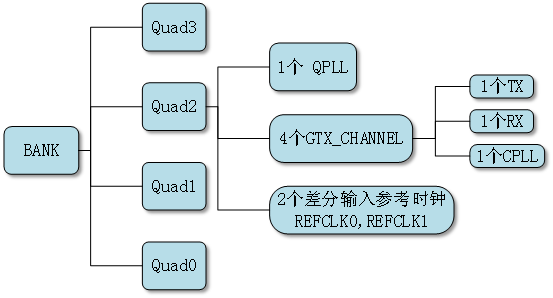

所以Kintex-7 FPGA(XC7K325T)中quad、channel、GTX相互關系如圖4所示。1個Quad中有2個參考時鐘(REFCLK0,REFCLK1),根據板卡設計圖可知具體使用REFCLK0還是REFCLK1,參考時鐘頻率應根據核心板實際晶振頻率來選擇。

圖4 quad、channel、gtx相互關系

4. 測試結果

通過新建IP核工程,為IBERT協議配置定義界面,IP核有一些預置的協議,如收發器線速率選擇,位寬選擇,收發器參考時鐘來源和頻率等。本設計SFP+來自Quad116,參考時鐘來自MGTREFCLK1_116。本設計將GTX收發器參考輸入時鐘作為其系統時鐘。之后例化,生成bit流文件,完成FPGA配置文件生成。按照測試原理,我們將SFP+的光纖模塊的TX和RX短接,如圖5所示。連接好硬件,將bit文件下載到硬件電路板。

圖5 硬件實物圖與連接

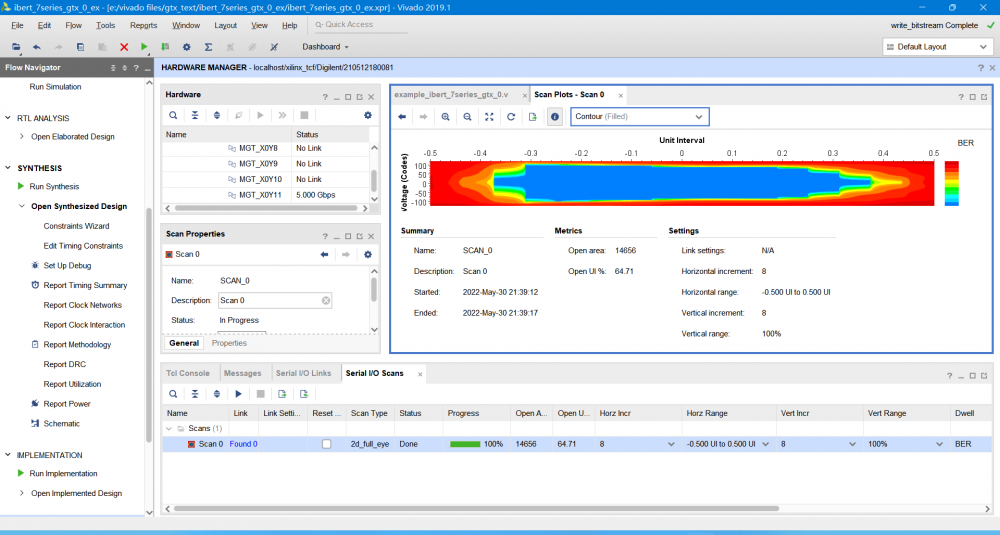

選擇需要查看眼圖的鏈路,眼圖參數可以使用默認參數,收發器眼圖測試結果如圖6所示。

圖6 測試收發器眼圖

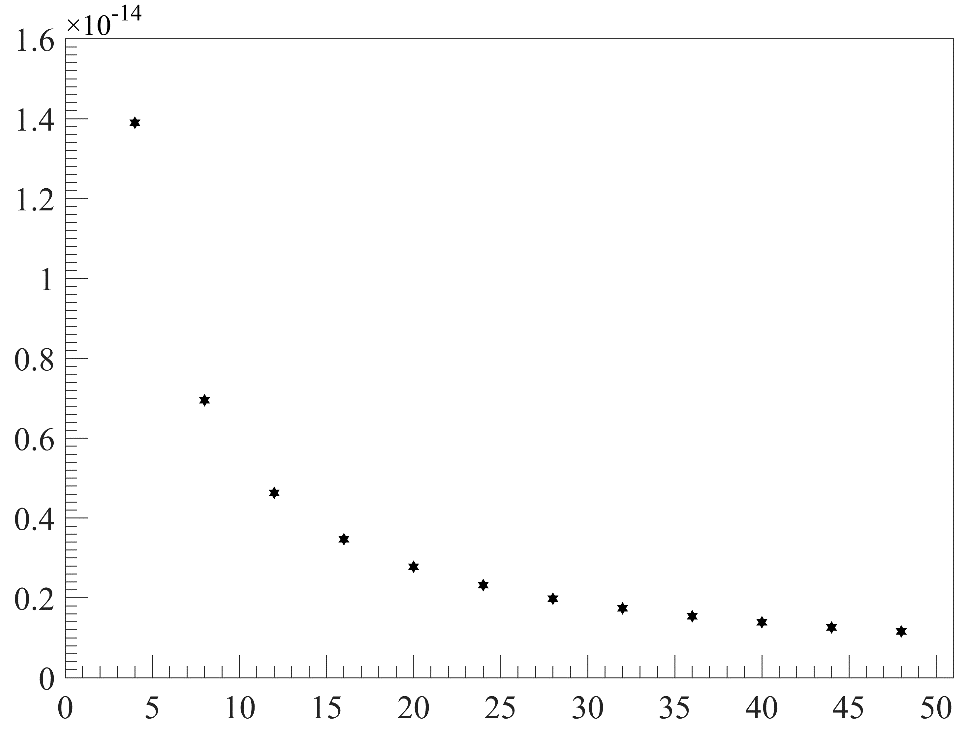

利用單根光纖將光模塊輸入輸出短接進行回環測試,使用IBERT IP核測試,通過Xilinx下載器將數據讀出。回環測試序列使用PRBS-31。每2小時記錄一次數據,總共測試48小時。測試結果如圖7所示,橫坐標為時間,連續運行48小時后,縱坐標為誤碼率,光纖通信誤碼率為2 × 10-15,速率穩定在5 Gbps,除去編碼開銷實際速率為4 Gbps,滿足一般的速率需求。

圖7 誤碼率測試

5. 總結

通過環回方式的誤碼率測試,可判斷出存在的問題以及測試出板卡實際支持的速率。IBERT可在運行過程中設置高速串行收發通道的各項參數,并提供了多種環回模式及多種測試激勵源,并可通過自動掃描測試,確定收發的最佳參數。可以滿足硬件測試時對高速串行收發通道信號測試的大部分需求,在故障定位等場合均可使用。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。