對比 | 三星與臺積電的多維度對比

據報道,三星計劃斥資1,160億美元用于其下一代芯片業務,其中包括為外部客戶制造芯片代工業務,以期在2022年之前縮小與行業領導者臺積電的差距。

三星的策略是雙重的:

1.2022年下半年將量產3nm芯片,以與臺積電匹配。

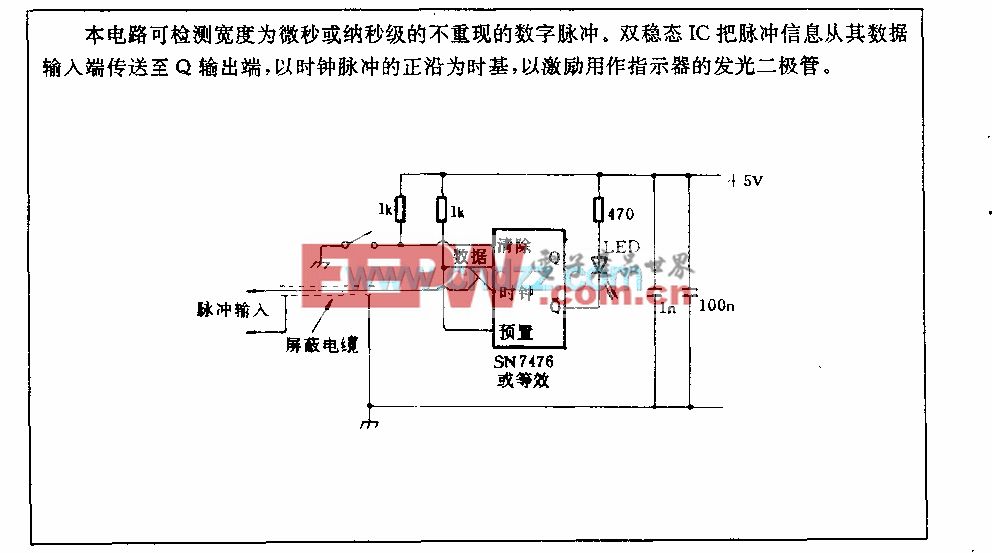

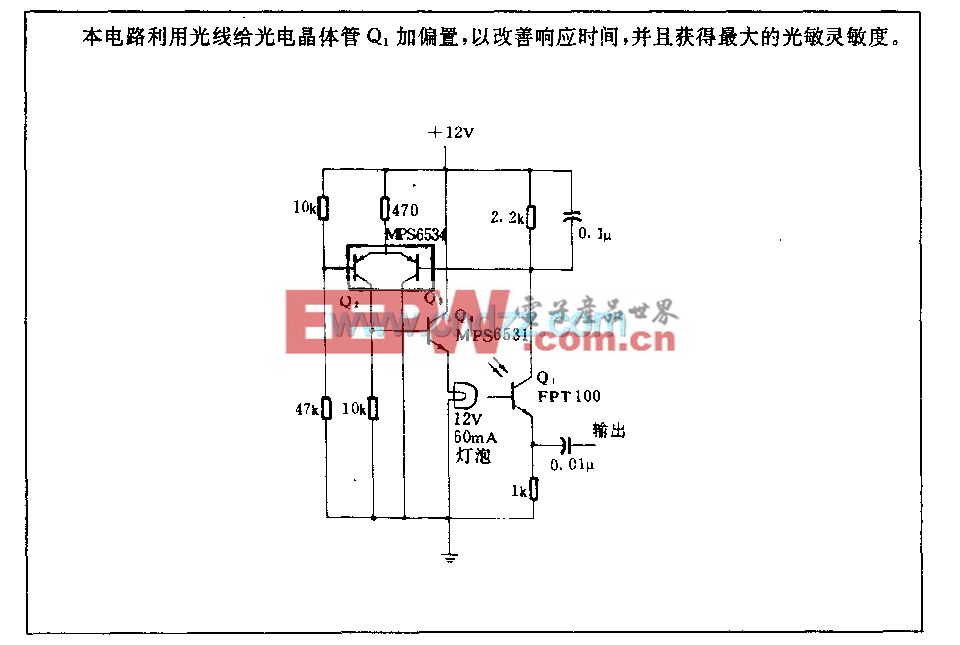

2.如圖1所示,采用更先進的全能柵極(GAA)技術代替TSMC的FinFET結構。

GAA在晶體管性能控制方面具有顯著優勢,因為它可以更精確地控制流經溝道的電流,縮小芯片面積并降低功耗。

與FinFETs不同,在FinFETs中,更高的電流需要多個并排的鰭片,而GAA晶體管的載流能力通過垂直堆疊數個納米片,柵極材料包裹在溝道周圍而增加。

三星聲稱,與7nm技術相比,其GAA工藝將能夠使芯片面積減少45%,功耗降低50%,從而使整體性能提高35%。

在IEEE國際固態電路會議(ISSCC)上,三星工程師分享了即將推出的3nm GAE MBCFET芯片的制造細節。三星表示,傳統的GAAFET工藝使用三層納米線構造晶體管,并且柵極相對較薄。此外,三星MBCFET芯片工藝使用納米片構造晶體管。目前,三星已經為MBCFET注冊了商標。三星表示,這兩種方法都可以達到3nm。

在本文中,我從技術,產能和資本支出重點探討了三星公司目前和未來的能力(三星存儲部門除外),以及三星是否確實能夠縮小7納米以下節點的差距。

三星3納米芯片的更多細節

三星晶圓廠將成為第一家在即將到來的3nm工藝中使用類似全柵場效應晶體管(GAAFET)結構的半導體制造商。雖然該節點尚未準備就緒,但在IEEE國際固態電路會議(ISSCC)上,三星晶圓廠的工程師分享了有關即將推出的3 nm GAE MBCFET(multi-bridge channel FET)制造技術的一些細節。

據介紹,有兩種類型的GAAFET:典型的GAAFET,這被稱為具有“薄”鰭的納米線。以及MBCFET,稱為具有“厚”鰭的納米片。在兩種情況下,柵極材料在所有側面上都圍繞溝道區。納米線和納米片的實際實現方式在很大程度上取決于設計,因此,一般而言,許多行業觀察家用術語GAAFET來描述兩者。但是以前它們被稱為環繞柵晶體管(surrounding-gate transistors :SGT)。值得一提的是,MBCFET是 三星的 商標。

1988年,全球首次展示了GAAFET,因此該技術的關鍵優勢眾所周知。這種晶體管的結構使得設計人員可以通過調節晶體管通道的寬度(也稱為有效寬度或Weff)來精確地對其進行調諧,以實現高性能或低功耗。較寬的薄片(sheets)可以在更高的功率下實現更高的性能,而較薄/較窄的薄片可以降低功耗和性能。為了對FinFET做類似的事情,工程師必須使用額外的鰭來改善性能。但是在這種情況下,晶體管溝道的“寬度”只能增加一倍或兩倍,這并不是很精確,有時效率很低。另外,由于不同的晶體管可以用于不同的目的,因此通過調整GAAFET可以提高晶體管的密度。

早在2019年,三星推出的的3GAE工藝設計套件版本0.1就包括四種不同的納米片寬度,以為早期采用者提供一定的靈活性,盡管目前尚不清楚該公司是否增加了寬度以提供額外的靈活性。但是三星表示,總的來說,與7LPP技術相比,其3GAE節點將使性能提高30%(在相同的功率和復雜度下),功耗降低50%(在相同的時鐘和復雜度下),并且晶體管密度提高了80%(包括邏輯和SRAM晶體管的混合)。

三星的3GAE(其第一代MBCFET技術)將于2022年推出。雖然三星目前尚未披露其所有特性。但該公司在ISSCC上討論了如何使用新型晶體管來提高SRAM性能和可擴展性。

近年來,SRAM的可擴展性一直落后于邏輯的可擴展性。同時,現代片上系統將SRAM的負載用于各種高速緩存,因此提高其可伸縮性是一項至關重要的任務。

據《EE Times》亞洲報道,三星代工廠在ISSCC上介紹了其256Mb MBCFET SRAM芯片,該芯片的尺寸為56mm2 。這意味著盡管該公司尚未推出其首款3GAE邏輯芯片,但顯然該技術適用于SRAM。

SRAM是一個六晶體管存儲單元:兩個傳輸門(pass gates),兩個上拉和兩個下拉。在FinFET設計中,SRAM單元將使用具有相同溝道寬度的相同晶體管。借助MBCFET,三星可以調整溝道寬度,因此提出了兩種方案:在一種情況下,三星將溝道更寬的晶體管用于傳輸門和下拉電路,而在另一種情況下,三星將使用具有較寬溝道的晶體管用于傳輸門和晶體管。

至于較窄的下拉通道。三星通過IEEE Spectrum稱,通過將具有更寬溝道的晶體管用于傳輸門,并將具有較窄通道的晶體管用于上拉,與常規的SRAM單元相比,三星設法將寫入電壓降低了230 mV 。

三星與臺積電的支出和產能

三星是否有能力在臺積電主導的市場中占據重要份額?這是一個很復雜的問題。因為臺積電本身在2021年花費了創紀錄的250億美元,以確保它保持在技術和產能的前列。

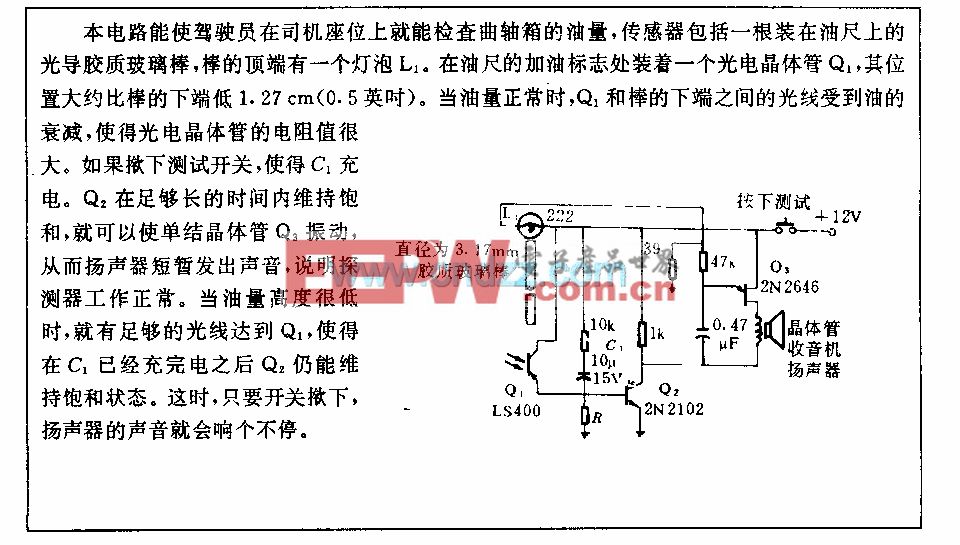

表1列出了臺積電和三星晶圓代工部門所有節點的總產能。從積極的一面來看,臺積電的產能比例從2016年的3.3倍降至2021的2.3倍。

表1中的數據顯示,臺積電在產能方面遠遠領先于三星,但價差略有下降。原因之一是三星的資本支出增加,如表2所示,該公司在2020年的制造資本支出同比增長了85%,并計劃在2021年進一步增長32%。相比之下。臺積電在2020年的資本支出變化為-7%,但在2021年將增長49%。

表3顯示了7TSMC和Samsung在7nm以下節點的產能對比。在2019年和2020年,臺積電在7nm節點的產能大約增加了5-6倍,到2021年的預測是3.5倍。在5納米節點,臺積電的產能大約增加了四倍。

為了彌補5nm和3nm的有限產能,三星正推進先進的邏輯體系結構,我之前已經討論過,請讀者參考圖1。

臺積電擁有460多個客戶,其領先的客戶名單包括蘋果,博通,海思半導體,AMD,聯發科,NVIDIA,高通和英特爾等頂級無晶園公司和IDM。

表4顯示了這些公司及其在2019-2021年臺積電收入中所占的百分比。

至于三星,將其客戶群與臺積電進行比較有點誤導。2020年,三星將其晶圓代工廠產的60%用于內部使用,主要用于智能手機的Exynos芯片。其余產能來自非專屬客戶,高通(20%),其余20%來自Nvidia,IBM和英特爾。隨著三星在2021年增加其低于7納米的產量,自用產能占比將降低,可能降至50%。

三星和臺積電爭霸戰開打

據分析機構ICinsights報道,在過去的25年中,跟上前沿IC技術的發展步伐變得越來越昂貴。現在,為邏輯器件實施最先進的工藝技術所需的投資已將大部分公司已經趕出了市場,僅剩下三星,臺積電和英特爾這三家公司。而在這三家制造商中,只有兩家可以真正地處于領先地位,那就是三星和臺積電。

從現狀看來,他們都可以批量生產7nm和5nm IC。相比之下,預計直到2022年,英特爾都不會在自己的制造工廠中大批量生產7nm器件,而屆時三星和臺積電預計已經推出3nm制程技術生產商業量的IC。

從歷史上看,具有最高資本支出水平的IC公司也是能夠生產最先進芯片的公司。盡管在過去27年中,英特爾已連續25年位居半導體行業前兩大資本支出者之列(圖2),但該公司在2020年的支出僅是三星當年支出的一半左右,而且預計將再次遠低于三星支出的一半。三星和臺積電預計今年將各自支出約280億美元。

在2010年,三星的半導體資本支出花費首次超過了100億美元。在2016年,公司在半導體資本支出上花費了113億美元,然后在2017年,三星半導體集團的支出增加了一倍以上,達到242億美元。

自2017年以來,三星的半導體資本支出一直非常強勁,2018年的支出更是達到驚人的216億美元,2019年達到193億美元,去年達到281億美元。 在半導體行業的歷史上,三星在2017-2020年期間的龐大支出(932億盡管三星尚未為其2021年的支出提供指導,但IC Insights估計該公司的支出將基本與2020年持平。

臺積電是唯一提供領先技術的純晶圓代工廠。它對7納米和5納米工藝的需求非常強勁,這些工藝占其2H20銷售額的47%。它目前的大部分投資都針對其7nm和5nm技術的額外產能。

臺積電的5nm產品占到2020年總銷售額的8%(35億美元),由此可以說明去年臺積電轉向了更先進的工藝有多快,因為該公司在去年上半年基本上沒有5nm收入。

現在看來,三星和臺積電都意識到了眼前的千載難逢的機遇。

三星在2017年開始支出激增,臺積電也將在2021年開始大規模的多年支出增長。ICInsights預計,三星和臺積電今年的資本支出將至少達到555億美元,占總支出的5%。前兩個支出最多的時間是半導體行業總支出中的高百分比(圖3)。

由于目前尚無其他公司能夠與這些龐大的支出相匹敵,因此三星和臺積電今年可能會在先進集成電路制造技術方面與自身和競爭對手展開更大的距離。

像歐盟,美國和中國這樣的政府能否投資于其本土IC產業并趕上與三星和臺積電(TSMC)的IC技術競賽?

考慮到差距還很大,IC Insights認為,各國政府至少需要在至少五年內每年花費至少300億美元,才能獲得合理的成功機會。他們是否有意愿和/或能力兌現這一承諾?

此外,對中國而言,即使有錢,也肯定會受到貿易問題的阻礙,因為貿易問題禁止一些最關鍵的過程設備出售到中國。

如果沒有其他IC生產商或政府采取迅速而果斷的行動,三星和臺積電就將成功占領世界領先的IC工藝技術,這是未來先進的消費,商業和軍事電子系統的基石。

總結

三星比臺積電落后一代,后者預計將保持5nm和3nm的領先地位。

EUV系統的不足是臺積電在三星方面領先一代的催化劑。到2020年,三星電子總共購買了25臺EUV光刻系統,而臺積電則購買了約50臺。

在短期內,有幾個緩解因素將保持這一差距:

- ASML的生產限制為每年約50個EUV系統

- ASML還有其他要分配系統的客戶,包括SK海力士,英特爾,美光科技和可能的中芯國際

- 三星還必須分配資本支出用于其DRAM部門的EUV購買

由于三星不是臺積電(TSMC)這樣的純晶圓代工廠,其7納米以下的產量中至少有50%被分配給其智能手機內部使用,這將限制其客戶群,因為其產能增長將因缺乏EUV而受到阻礙系統。

三星將通過過渡到3nm的GAA和MBCFET等高級邏輯架構,逐步縮小技術差距。GAA的功耗降低了50%,整體性能提高了35%,這將推動客戶向三星遷移,只要有可用的容量。但是產能缺口仍將存在。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。