- 不管是跨州運送一整列散裝產品、通過長長的雙層集裝箱列車運輸制成品,還是用鐵路罐車將有毒化學品運送到工業園區,或通過繁忙進出于都市的市郊列車來運送旅客,都必須要保證火車按照時刻表在鐵軌上正常行駛。Fluke

- 關鍵字:

火車 保持 溫度測試

- 摘要:為滿足能譜分析中多道脈沖幅度分析器A/D轉換的要求,設計了一種高速脈沖峰值保持電路。以高速電壓比較器LM311、采樣/保持芯片LF398作為主要器件,具有幅度判別、波形采樣、峰值保持、電荷泄放等功能,結構簡

- 關鍵字:

電路 設計 保持 峰值 脈沖 高速

- 引言

現代高速運算放大器 (op amps) 的建立時間都為幾納秒左右。這個時間是如此的短暫。因此,要想在某個合理誤差范圍內對其進行測定,不僅僅對自動測試設備(ATE)是一個難題,即使在工作臺上也難以完成。今天的運

- 關鍵字:

采樣 保持 技術實現 測定

- 1 引言 測量儀器、數據采集系統、伺服系統以及機器人等重要單元或關鍵部件需在非正常掉電時進行狀態記錄和必要的系統配置,使用電池往往由于長期浮充致使壽命減少,且需定期更換。超級電容器(Supercapacitor)兼

- 關鍵字:

保持 后備 電源 電容 超級 高效 Boost 長壽

- 在一個高級駕駛輔助系統的攝像機系統即像在夜間也能夠在屏幕上顯示車前方和后方的狀況。它能夠分析視頻內容,用于進行車道保持和長/短距光頭燈控制。

一個圖片傳感器將輸入的視頻車架提供給單核或雙核架構,并通過

- 關鍵字:

飛思卡爾 燈控 車道 保持

- 保持心臟設備市場的設計成本、低功率和功能之間的平衡,目前心血管疾病已經成為全球最主要的死亡原因。據估計,2005年約有1750萬人死于心血管疾病,這占全球死亡人數的30%左右。而在這些死亡人數中,760萬人死于心臟病發作,570萬人則死于中風。截止2015年,預計每年將有2

- 關鍵字:

保持 設備 低功率

- 有些應用需要對一組模擬電壓的采樣,至少有兩種傳統方法可以滿足這種要求。最常見的辦法是將一個經典的模擬累加器與一個采樣保持放大器級聯。經典的模擬累加器是一個運放加上至少三只精密電阻。這些電阻的值應盡可能

- 關鍵字:

雙輸入 采樣 保持 放大器設計

- 電路的功能無需放大直流信號時,在輸入電阻上串聯一個隔直電容C1,可使偏置漂移忽略不計。這樣即使放大器交流增益比較高,輸出仍然是直流工作,OP放大器只作為單純的放大元件使用。采用R3=R2來實現輸入電流偏置,但由

- 關鍵字:

增益 保持 偏壓 交流

- PLC內部掉電保持寄存器的應用,我們在設計小型的PLC控制系統時,常常會需要在外部改變PLC內部的數據,譬如Counter, Timer或者Data的值,以適應生產過程的需要。而且要求系統關機以后,這些數據還能夠保存在PLC內部,當下次開機后,這些數據可以被調

- 關鍵字:

應用 寄存器 保持 內部 PLC

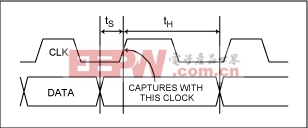

- 摘要:本應用筆記定義了高速數/模轉換器(DAC)的建立和保持時間,并給出了相應的圖例。高速DAC的這兩個參數通常定義為“正、負”值,了解它們與數據瞬態特性之間的關系是一個難點,為了解決這些難題,本文提

- 關鍵字:

保持 時間 建立 DAC 高速 轉換器 解讀

- 隨著用戶對手機功能的要求日益增長,一項新的需求進入手機制造商的考慮中,即手機可以有提供狀態的LED提示,以便在待機的同時,提醒用戶注意有未讀消息、即將到來的約會安排或者其它通知。最近發布的幾款手機甚至

- 關鍵字:

保持 待機 時間 影響 同時 指示燈 激活 手機 LED 如何

- 新設計的芯片內部電極的制造工藝對位置控制更為精確,進而生產出高Q值的0402和0603系列中的積層電感MLG0402Q和MLG0603P系列。積層電感采用鐵氧體或其它材料制成的薄片,并在薄片上用金屬漆(一般為銀)印制出繞線圖案而制成。將這些薄片排列成多層并創造出螺旋式內部電極結構。

- 關鍵字:

積層電感 保持 高頻電路 干擾

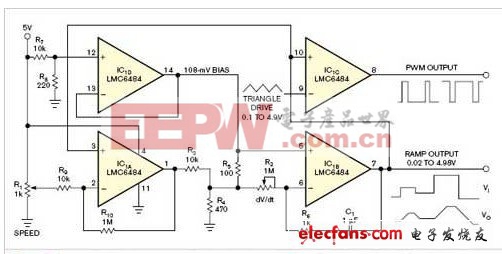

- 最初為控制模型火車而設計, 積分器斜向上或下,以預設比率響應輸入直流水平的改變,并保持電路輸入電壓水平。 運放積分器可以斜上升到飽和狀態,電容放電式開關會重置積分器。或者,三角波發生器應用中,輸入轉換

- 關鍵字:

水平 輸出 保持 向上 積分

- 本文介紹的LED驅動器參考設計為一串正向偏壓高達60V的LED提供700mA恒流驅動。本設計可基于電源斬波進行PWM調光。輸入電源以300Hz至1kHz的頻率斬波控制通、斷,實現LED亮度調節。驅動器采用固定頻率進行boost轉換器

- 關鍵字:

boost LED 電源斬波 保持

- 本文設計了一個可用于12 bit,20 MS/s流水線ADC中的采樣/保持電路。該電路使用CSMC公司的0.5μm CMOS工藝庫,在20 MS/s采樣頻率下,當輸入信號的頻率為9.8193 MHz時,SFDR為76 dB,精度達0.012%,完全滿足12 bit要求。本文運用增益增強型折疊式運算放大器,以獲得較高的增益和帶寬。同時采用柵壓自舉開關,并通過對電路中的開關組合優化,極大的提高了電路的線性性能;采用全差分結構、底極板采樣來消除電荷注入和時鐘饋通。該采樣保持電路能夠直接應用于高速高精度模/數轉換

- 關鍵字:

保持 電路 設計 采樣 ADC bit 流水線 適用于

保持介紹

您好,目前還沒有人創建詞條保持!

歡迎您創建該詞條,闡述對保持的理解,并與今后在此搜索保持的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473